SoC设计方法

Soc设计概述及流程

什么是SoC?

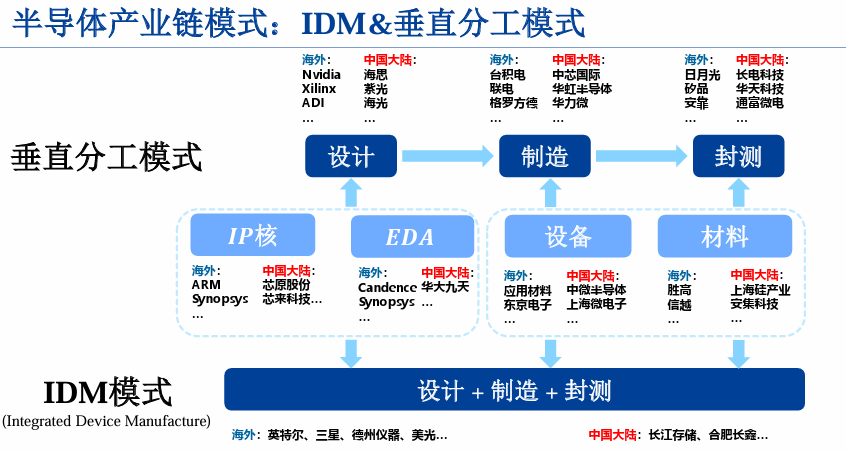

半导体产业模式及其基本分工:

SoC的基本概念:

SoC(System on Chip):系统级芯片,片上系统

SoC的诞生是集成电路领域发展的必然趋势。SoC的应用场景:

➢高性能计算

➢智能手机

➢汽车主控

➢物联网设备

SoC的优势

- 有利于复杂系统的集成

- 缩短设计时间

- 可靠性更高

- 延迟更低(内部连线短,传输延迟更小。内部晶体管阻抗低,较小的门延迟)

- 低能耗

- 低成本(IP复用)

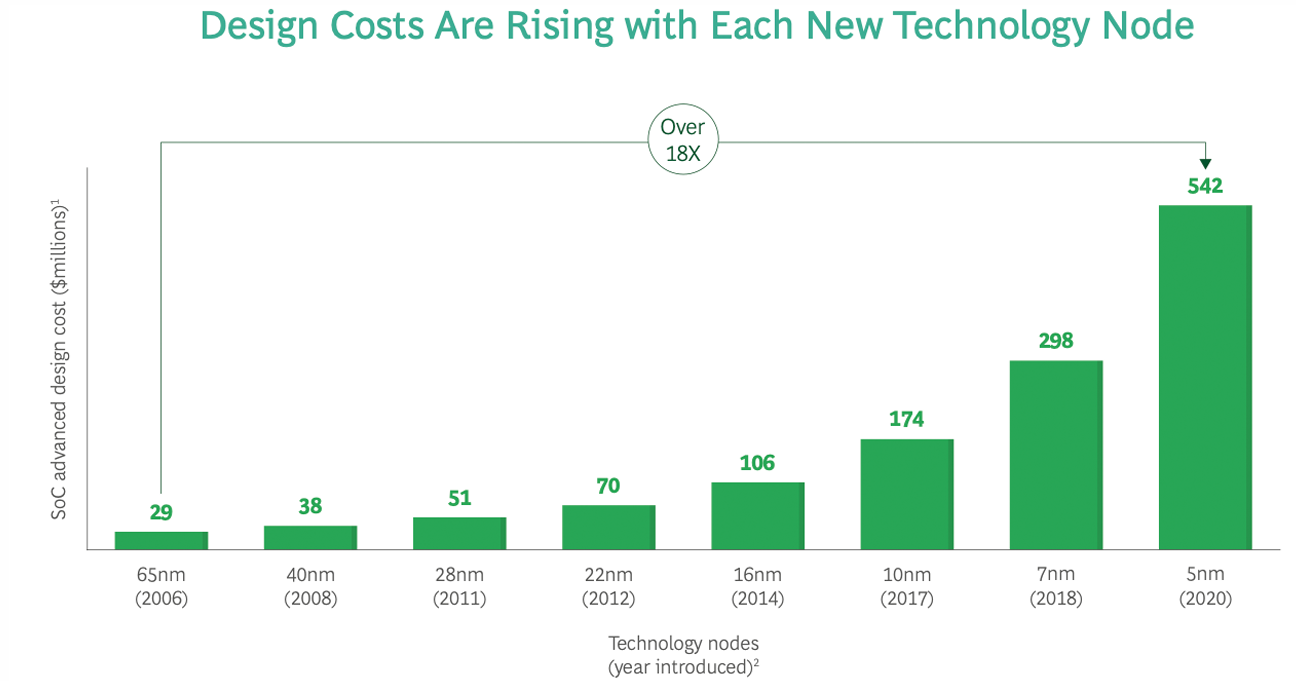

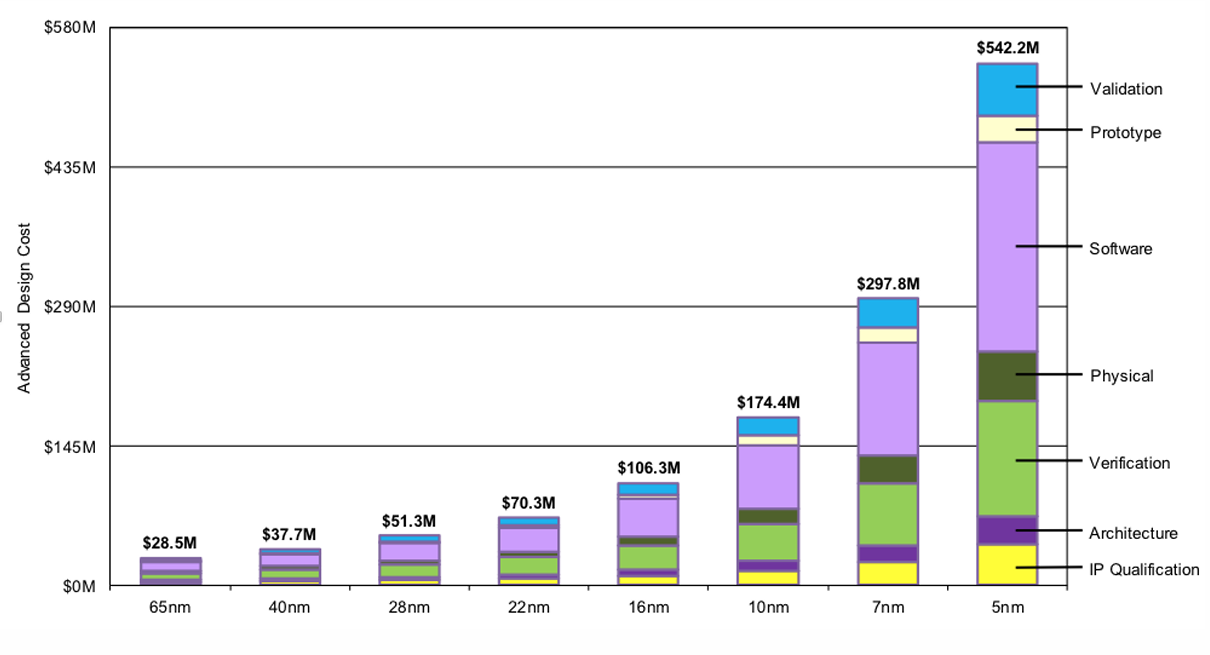

SoC发展的挑战

随着工艺节点的迭代,研发费用指数上升。

软硬件功能的划分(通用vs专用)

复杂性提升导致的验证难度提升

制造成本高(7nm工艺下,$400mm^2$的芯片良率只有大约55%),设计错误不可接受

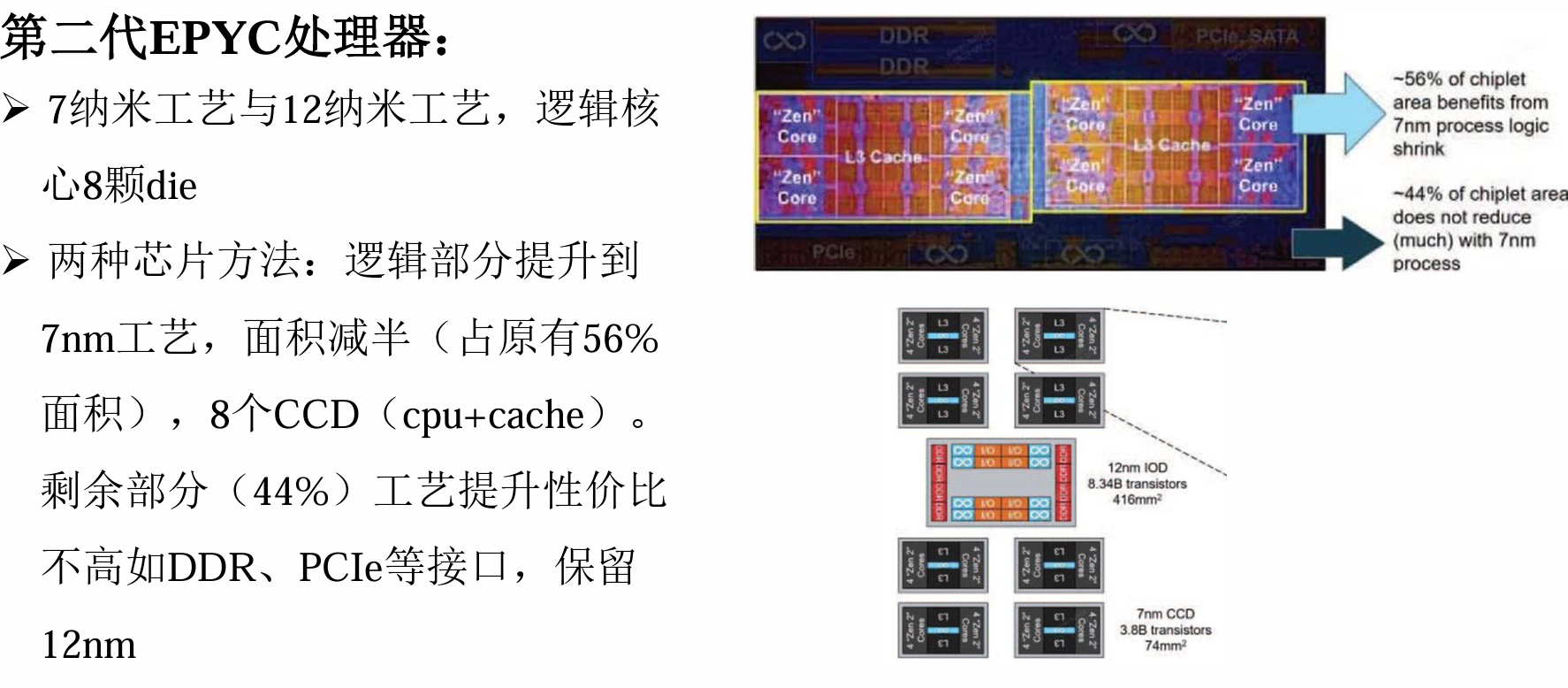

新型SoC: Chiplet

芯粒(Chiplet):将功能丰富面积较大的裸片(die)拆分成多个芯粒(chiplet)通过先进封装组合在一起形成一个系统芯片

SoC设计总结

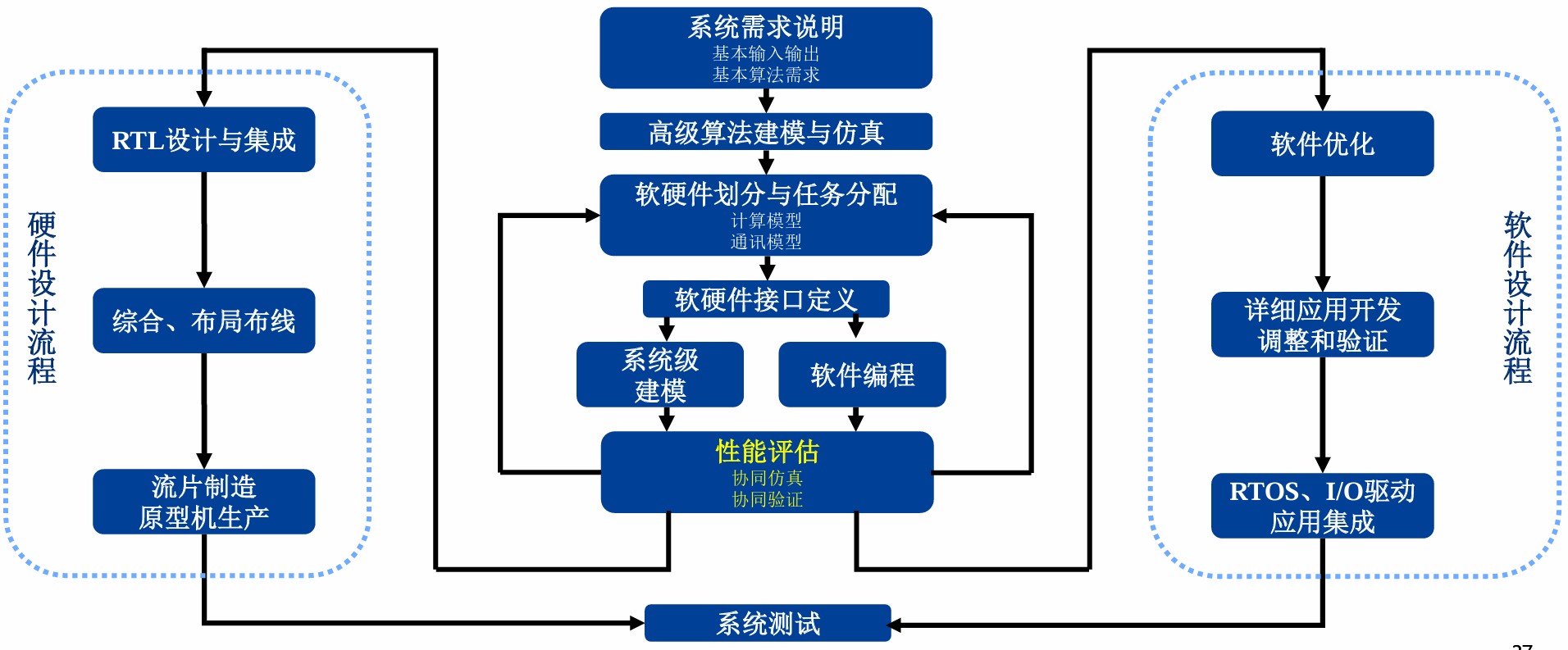

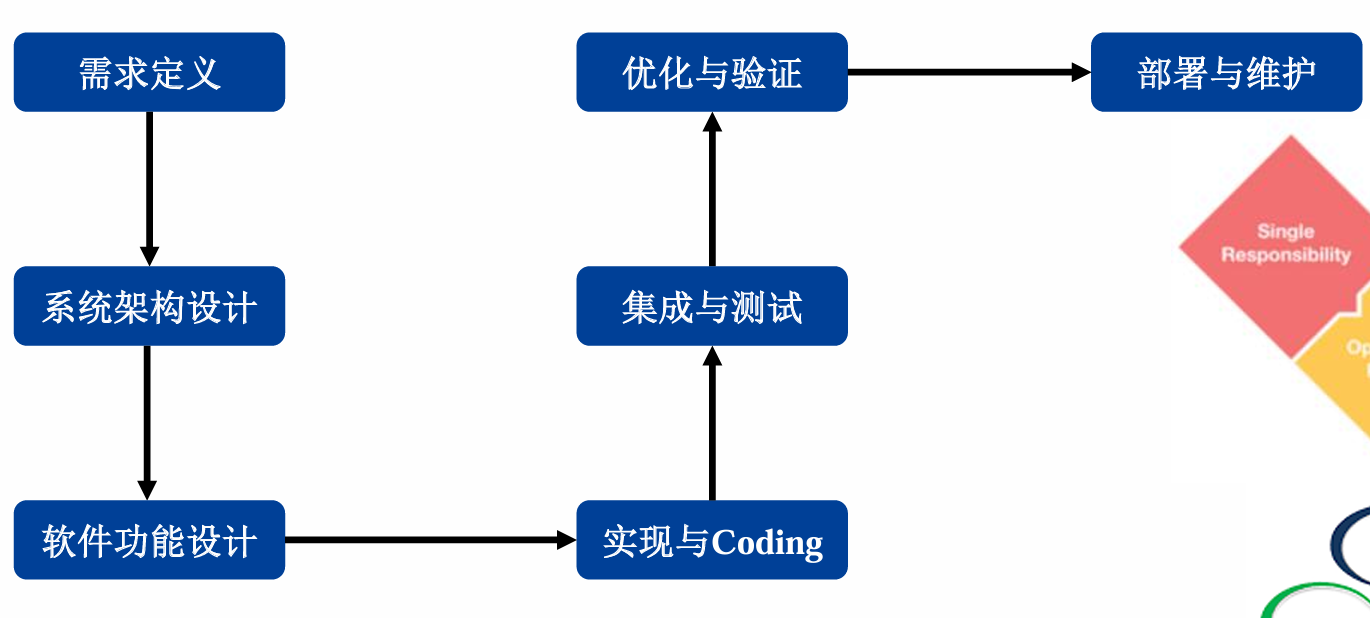

SoC设计流程

SoC系统是软件和硬件的结合,需要综合评估系统的性能,设计相应的硬件和软件架构:

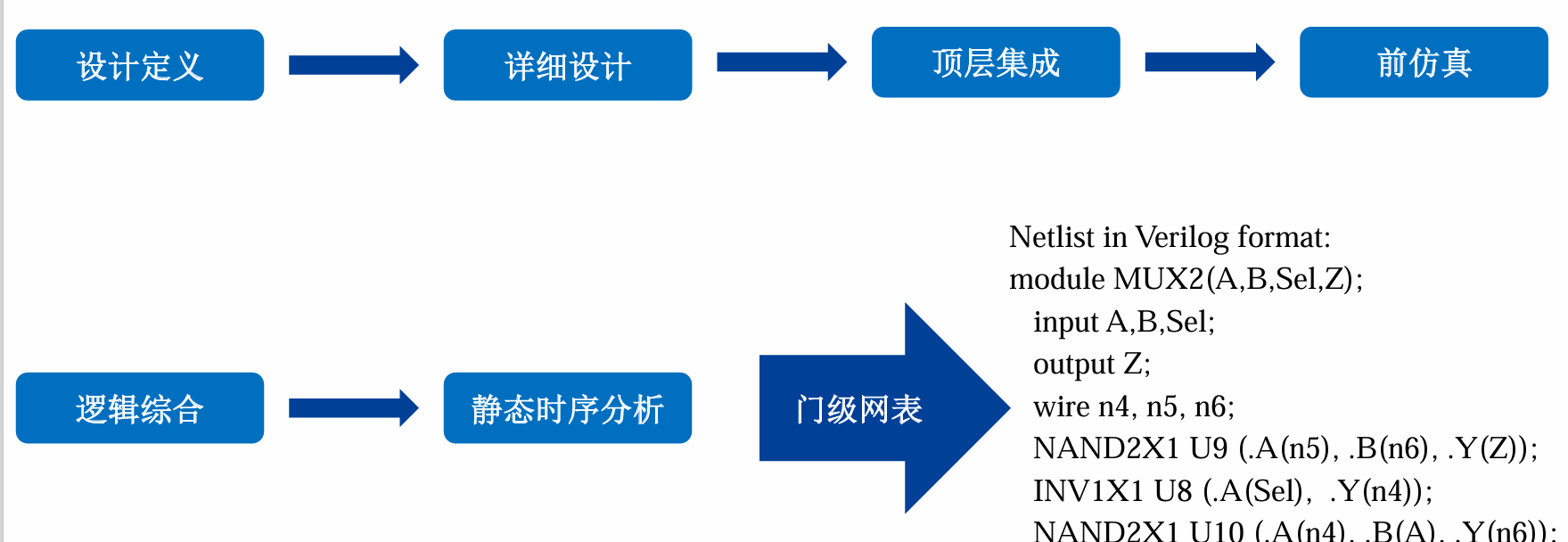

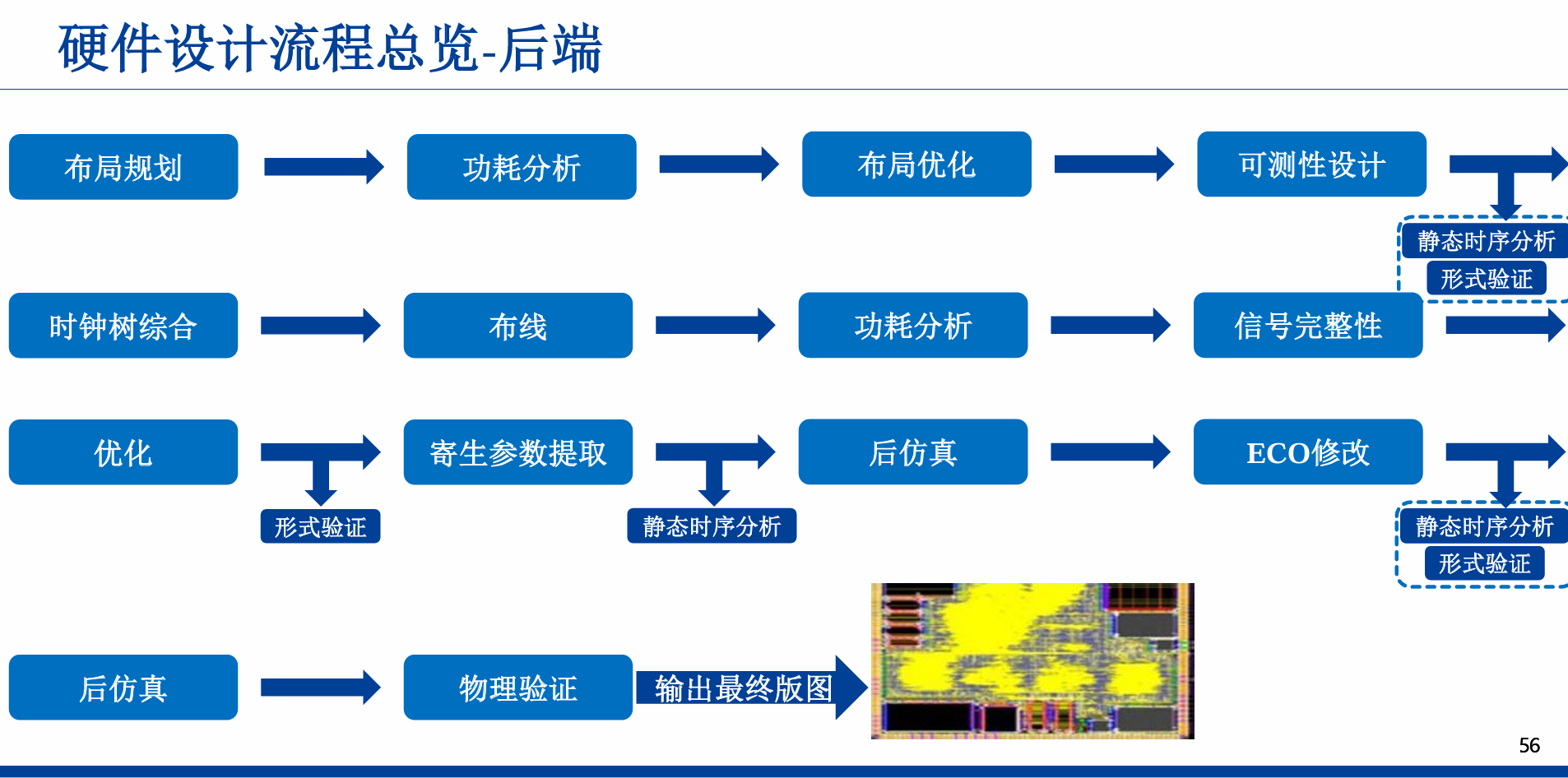

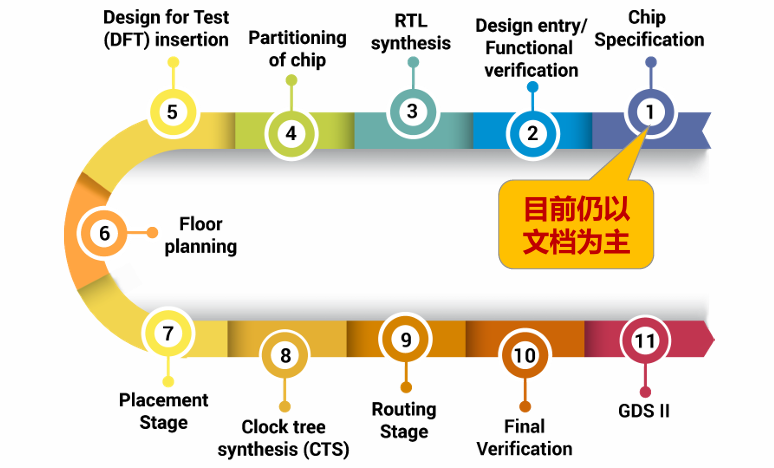

SoC的硬件设计流程

步骤基本可以分为:

- 设计规范(spec):确定芯片的顶层架构,规格参数,划分模块定义

- 模块设计与IP复用,顶端集成

- 前仿真:验证设计逻辑的正确性

- 验证

- 逻辑综合:代码翻译为电路(理想器件)

- 静态时序分析:检查设计是否符合时序要求,有无违例

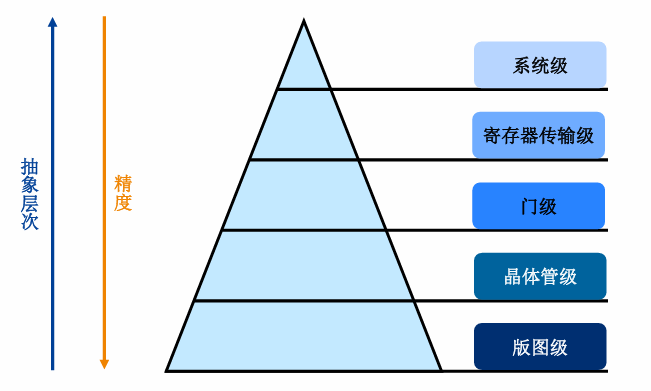

其中电路的抽象层次如下:

分别为:

- 系统级

- RTL级

- 门级(gate level)

- 集体管级(transistor level)

- 版图级 (lay-out level)

静态时序分析

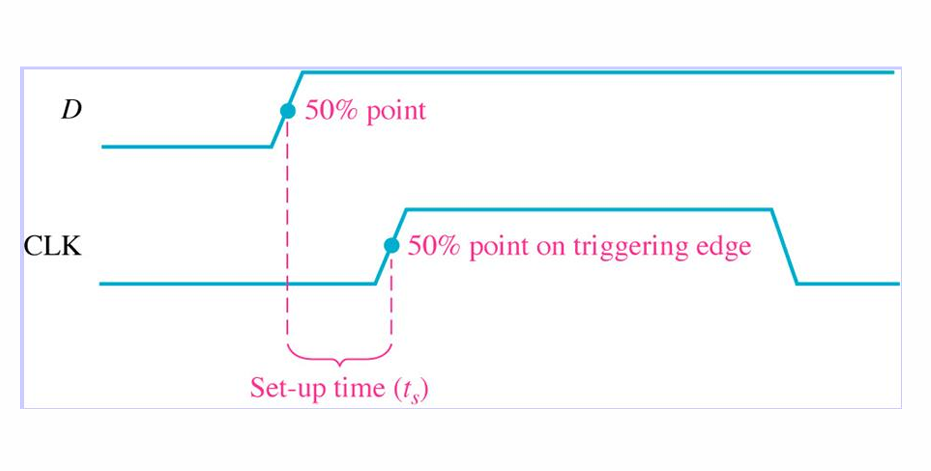

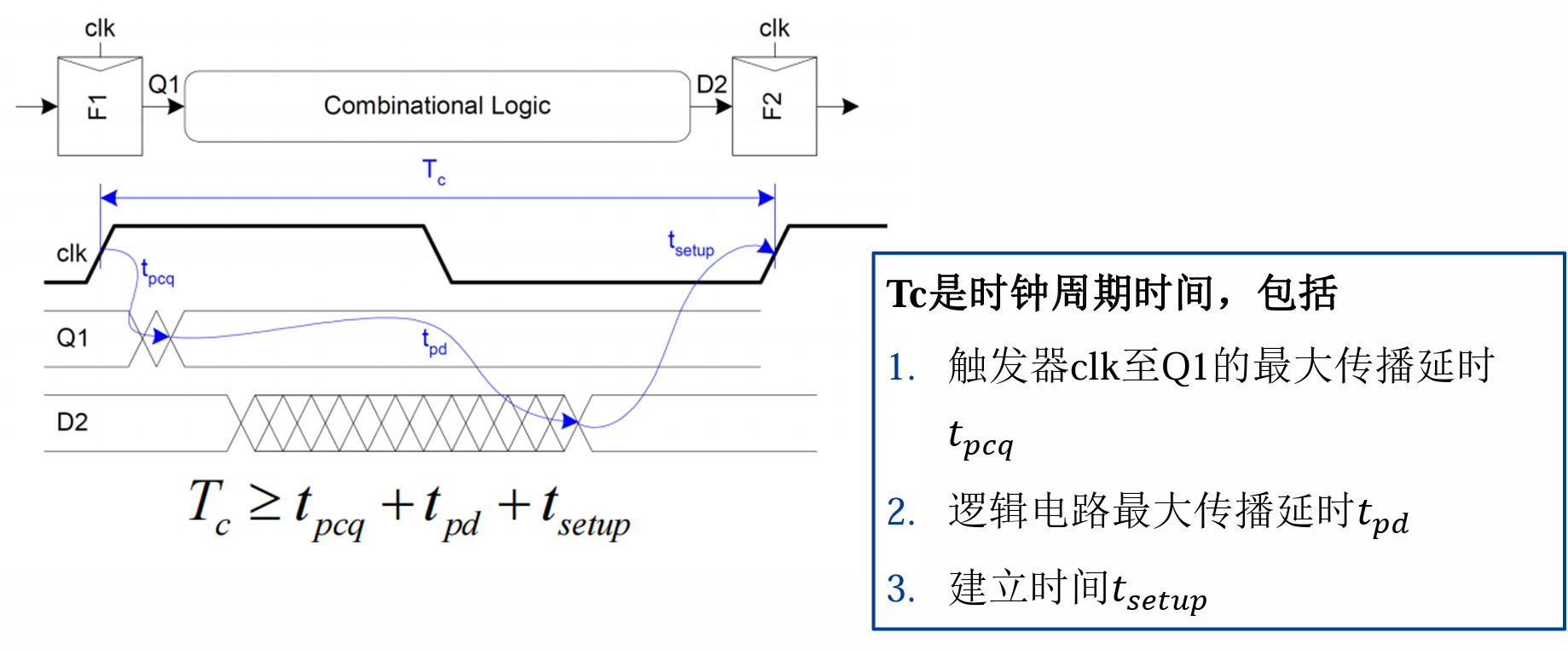

setup time 建立时间

在时钟信号到来之前,数据需要提前一段时间准备好。这个时间称为建立时间

如图,$t_{pcq}$指从时钟信号变化(50%)开始,到q端信号变化所需的时间(由寄存器本身的特性决定);

$t_{pd}$是组合逻辑的传输延迟。

由于在下一个时钟到来之前,下一级寄存器的输入数据应当准备好,因此有:

$T_c \geq t_{pcq} + t_{pd} + t_{setup}$

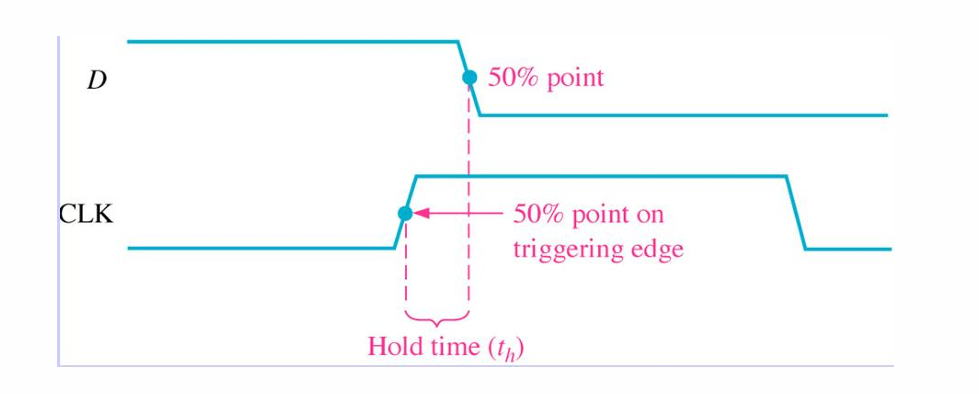

hold time 保持时间

在时钟信号变化之后,输入如数据不能立马跳变,而是需要保持原来的值一定时间,保证数据被完全写入寄存器。这个时间称为保持时间。

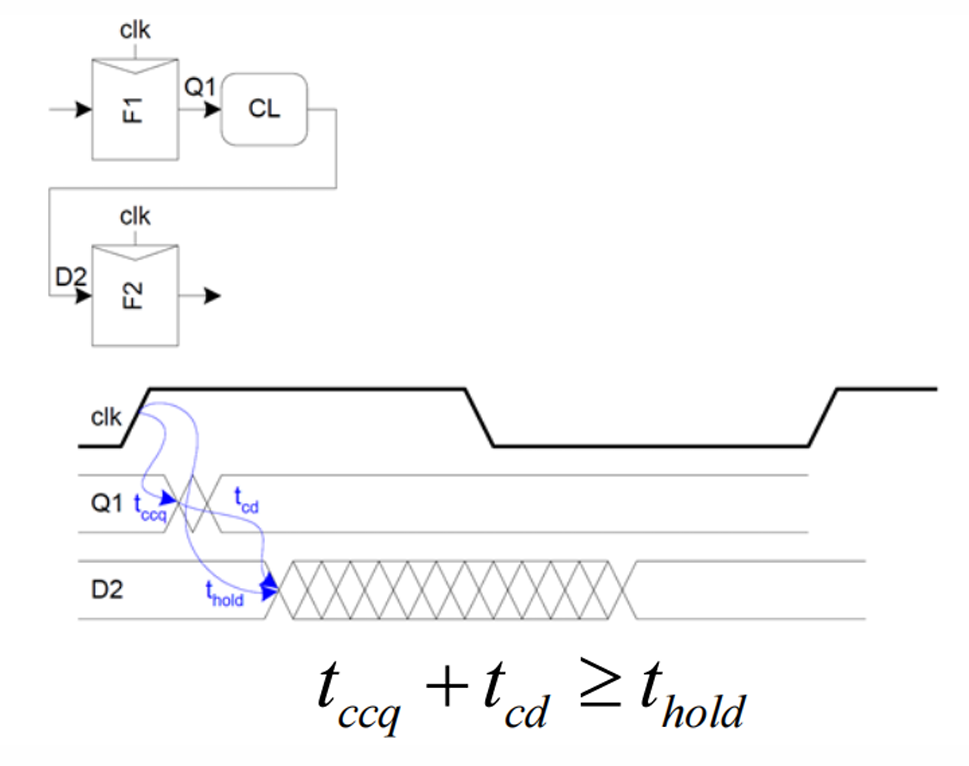

如图,对于理想时钟,clk总是同时到达。

$t_{ccq}$是时钟信号变化(50%)后,q1变化的时间。

$t_{cd}$是组合逻辑的传播延时,则从时钟变化后,经过$t_{ccq}+t_{cd}$的时间,D2的数据会发生变化。

按照保持时间的定义,需满足:

$t_{ccq}+t_{cd} \geq t_{hold}$

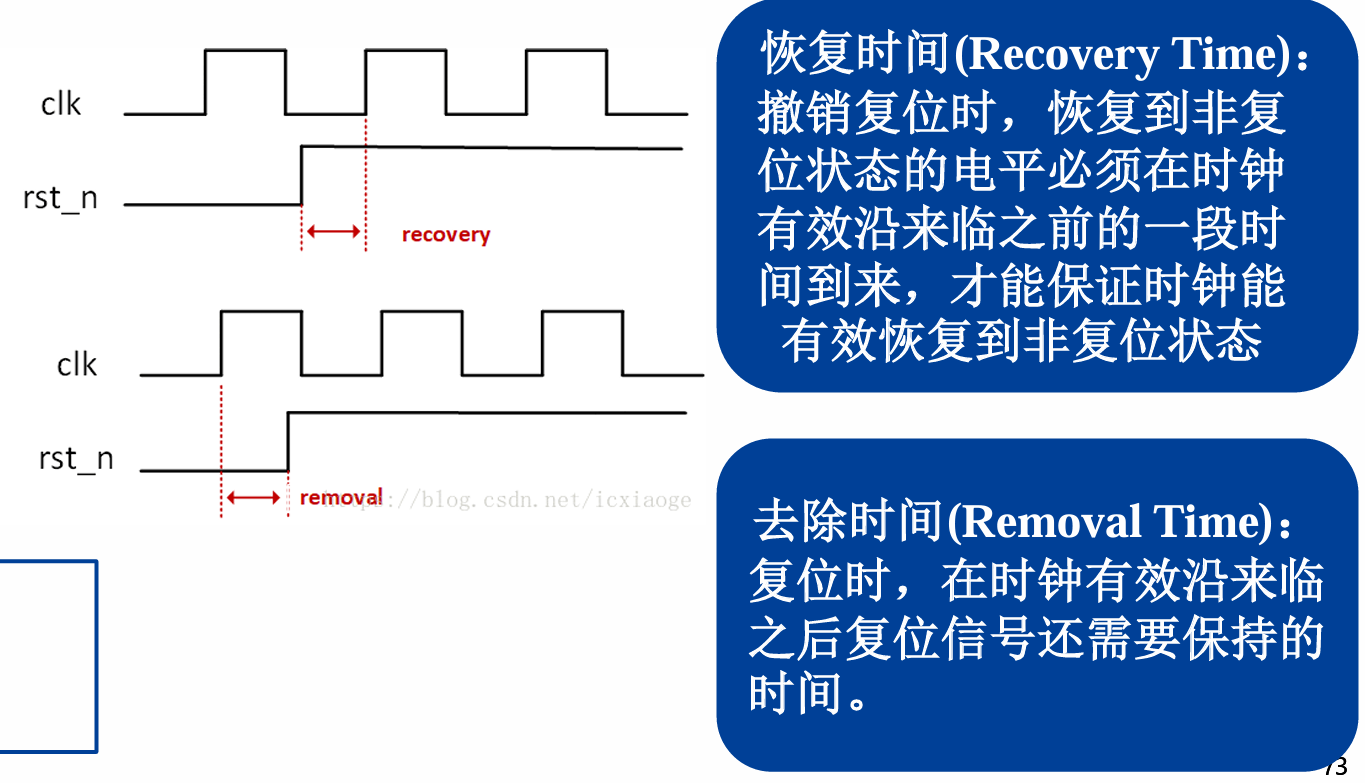

recovery/removal time

异步电路的复位信号,需要满足的时序关系:

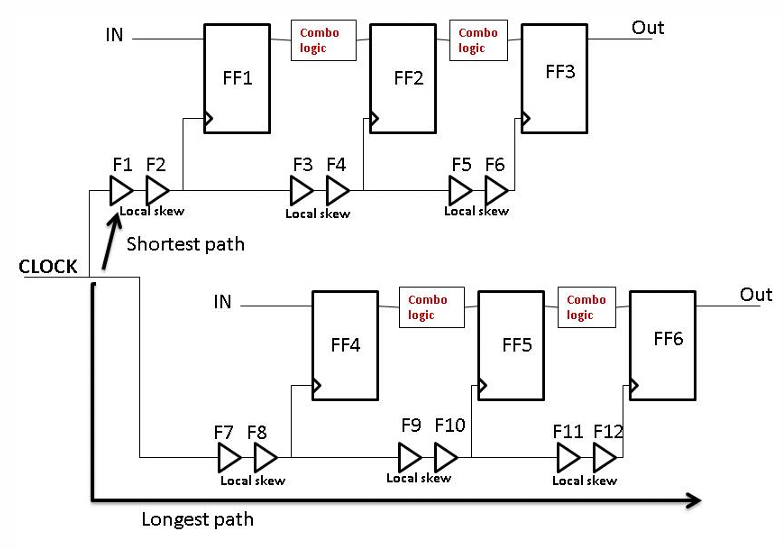

时钟偏斜 time skew

理论上clk对每个寄存器的clk端都应该相同,但实际上时钟到达每个元件的时间会有偏差,这个偏差称作time skew

可以通过插入buffer的办法尽量消除时钟偏向(时钟树综合)

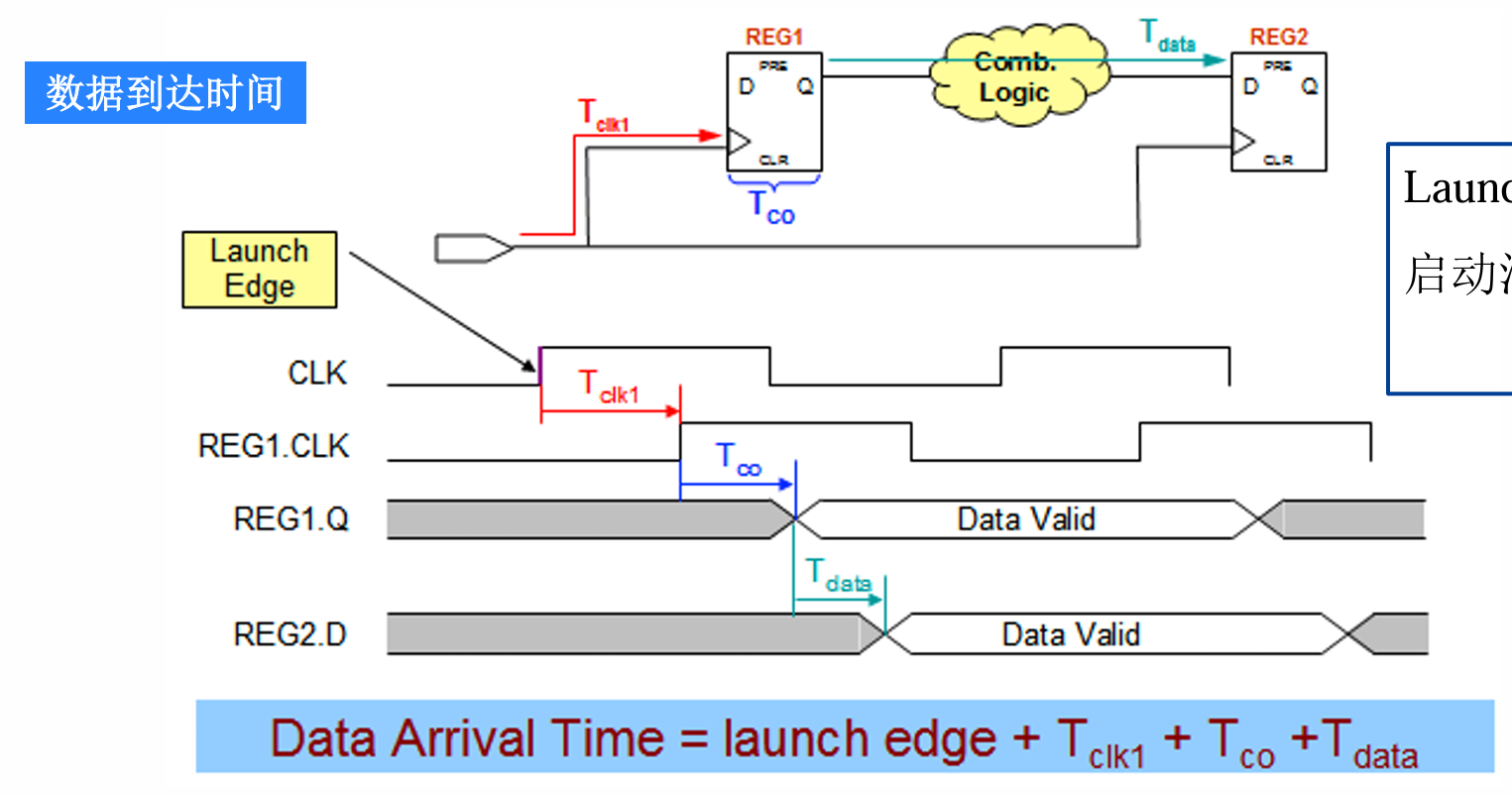

data arrival time 和 clk arrival time

分析第二个寄存器的D端,数据到达需要经过:

- 时钟启动时间(launch edge)

- clk1相对于时钟源的延迟$T_{clk1}$

- 寄存器的内部延迟(时钟变化到数据变化需要的时间)$T_{co}$

- 组合逻辑的数据延迟 $T_{data}$

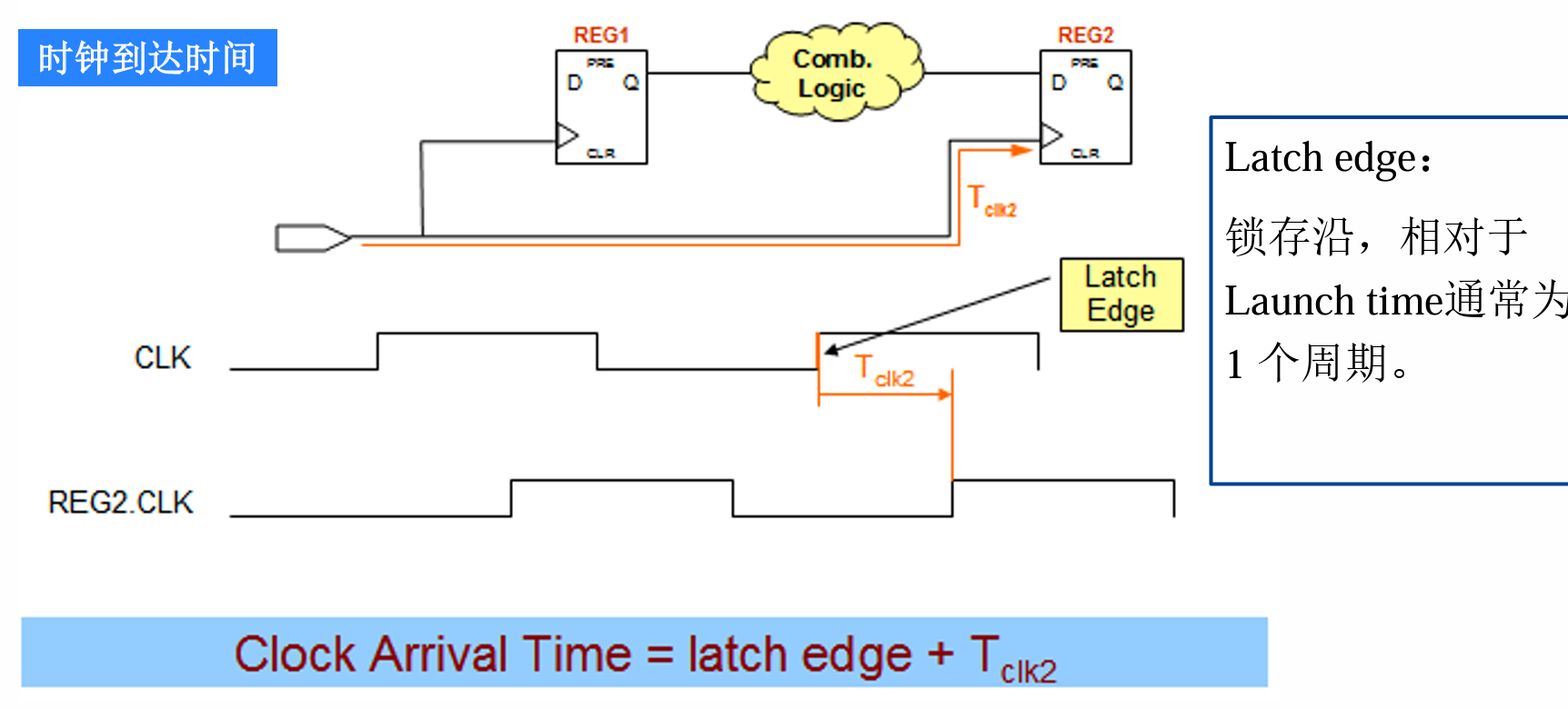

分析第二个寄存器的时钟到达时间:

- 时钟启动时间(launch edge)

- clk2相对于时钟源的延迟$T_{clk2}$

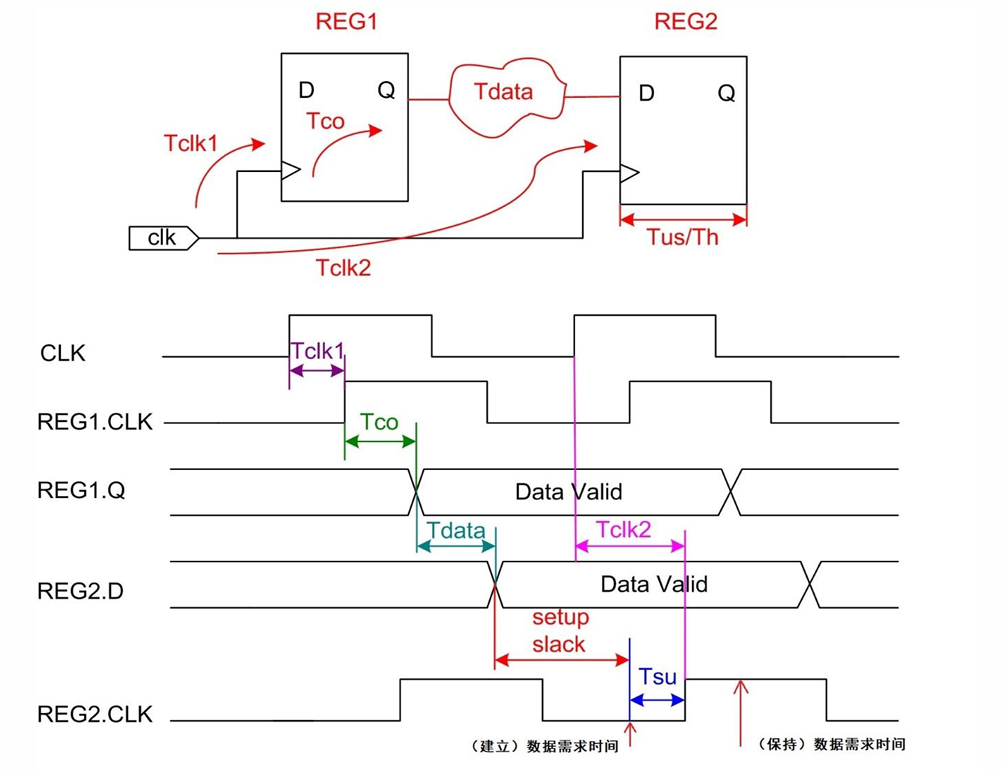

根据建立时间,数据需要提前于时钟到达,并保持稳定:

$data\ required\ time(setup) = clk\ arrival \ time - t_{setup} - setup\ uncertainty$

根据保持时间的定义,在时钟到达后,数据需要保持稳定一段时间:

$data\ required\ time(hold) = clk\ arrival \ time + t_{hold} + hold\ uncertainty$

时间裕量 time slack

对建立时间来说,由于数据应该提前到达,并保持一定时间的裕量,有:

$data \ arrival \ time(setup) + setup \ slack = data \ required \ time$

$setup \ slack = data \ required \ time - data \ arrival \ time \

= clk\ arrival \ time - data \ arrival \ time - t_{setup} - setup\ uncertainty $

set up slack应当大于0,才能保证时序正确。

对保持时间,时钟到达后数据需要保持一定的时间裕量,有:

$ data \ required \ time(hold) + hold \ slack =data \ arrival \ time$

$hold \ slack = data \ arrival \ time - data \ required \ time(hold)\

=data \ arrival \ time - clk\ arrival \ time - t_{hold} - hold\ uncertainty$

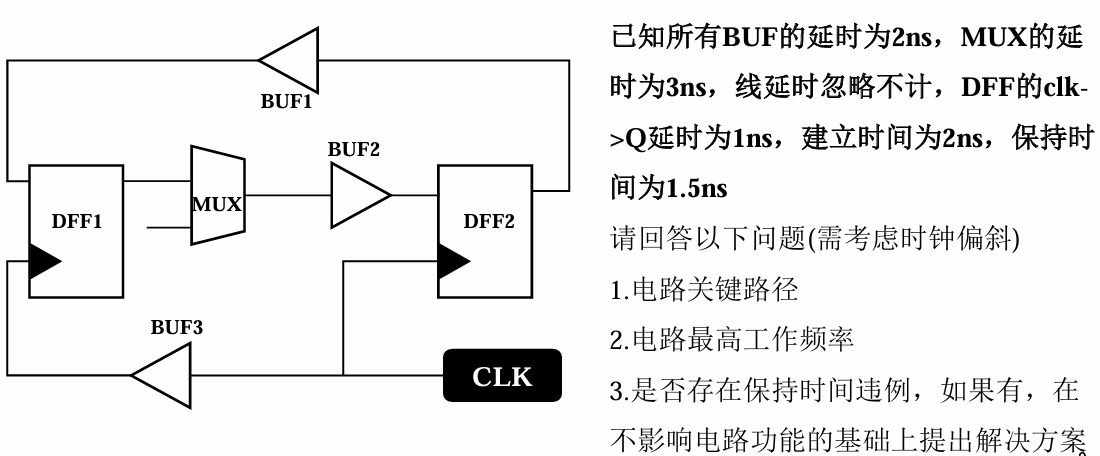

例

计算最大工作频率。 考虑建立时间,使 setup slack为0:

$T{clk_1}+ T_{co} + T_{data} + T_{setup} =T_{c} + T_{clk2}$

$f_{max} = \frac{1}{T_{co} + T_{data} + T_{setup} + T{clk_1} - T_{clk2}}$

SoC架构

SoC架构概述

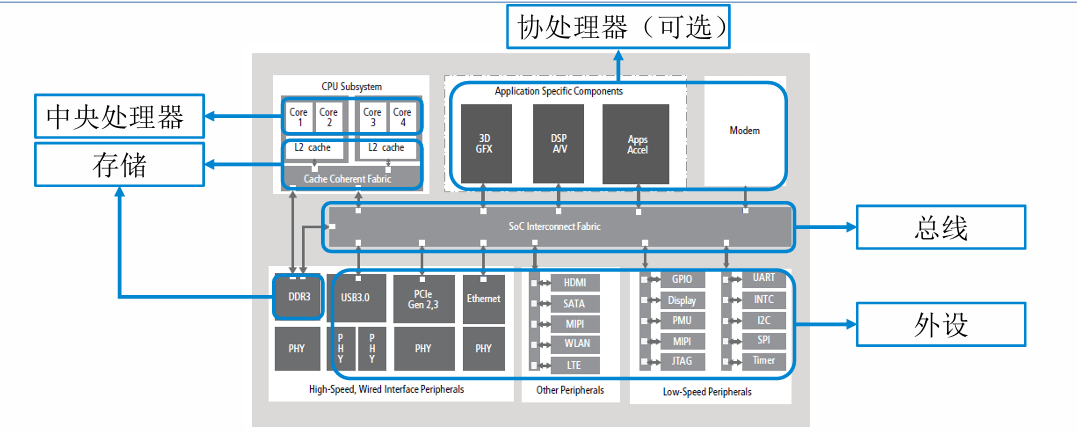

一个典型的SoC架构如下图:

SoC的同样遵循冯诺依曼架构,分别包括:

- 中央处理器(计算,控制)

- 存储系统

- 总线

- 外设 (I/O)

- 协处理器(可选,用于异构计算)

中央处理器CPU

略

系统总线

在SoC(System-on-a-Chip)系统中,总线是用来连接各个组件和模块,实现数据、地址和控制信号的传输。

常见的总线包括ARM公司的AMBA(advanced microcontroller Bus Architecture), 包括:

- AHB (Advanced High-performance Bus)

- AXI (Advanced eXtensibleInterface)

- APB (Advanced Peripheral Bus)

APB总线协议

(待补充)

AHB总线协议

(待补充)

AXI总线协议

(待补充)

接口控制模块

SoC一般包含多种不同的串/并接口,常见的有:

- SPI

- UART

- USB

- PCIe

此外还包括:

- 中断控制器(Interrupt Controller, INTC)

- 实时时钟(Real Time Clock, RTC) 、Timer、Watchdog

- 功耗管理模块(Power Management Controller, PMC)

等功能模块。

串/并行通信接口

串行/解串器

PCIe (Peripheral Component Interconnect Express)

SPI (Serial Peripheral Interface)

UART (Universal Asynchronous Receiver/Transmitter)

USB (Universal Serial Bus)

中断控制模块

(待补充)

时钟外设

(待补充)

功耗管理模块

(待补充)

Lecture 3 系统级建模

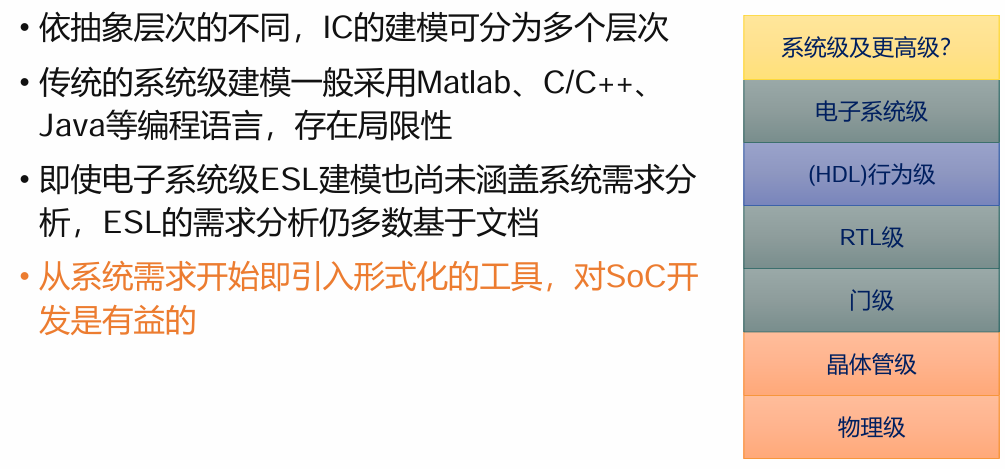

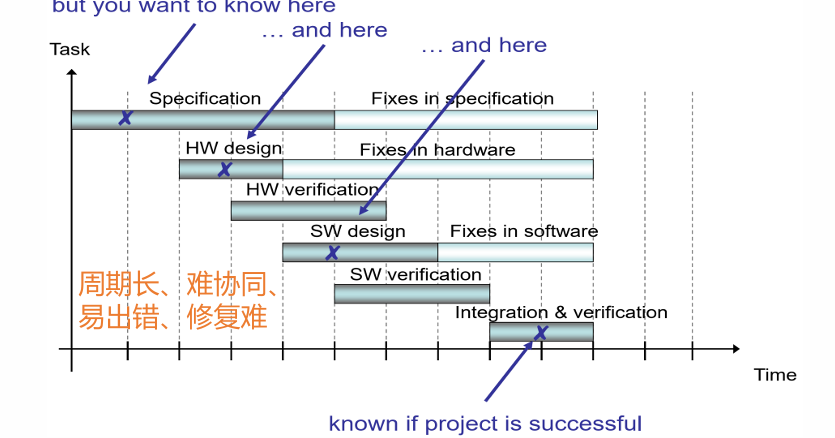

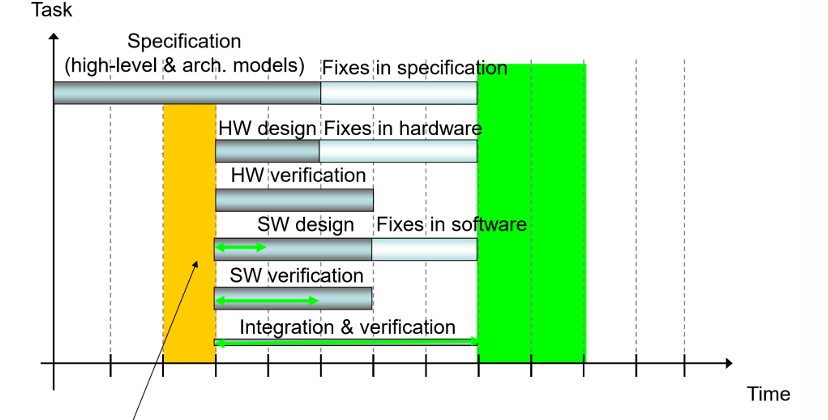

在传统的top-down设计流程中,其余环节都可以比较好的形式化,量化,然而顶层的功能需求定义等工作还是依赖文档和设计者对于文档的理解。

通过加强系统级建模,可以更好的克服非形式化手段带来的不精确性,有效将需求转化为产品。

系统级建模ELS

通过更高层次的建模来提高开发效率

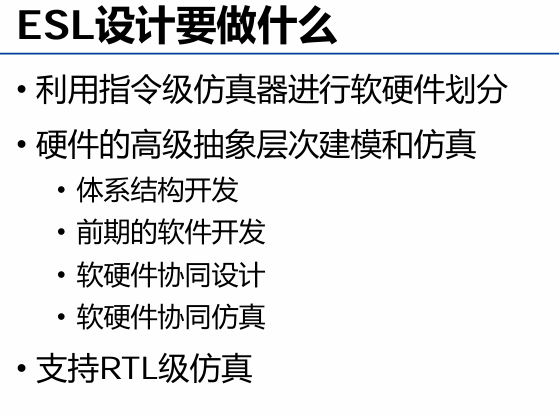

ELS功能:

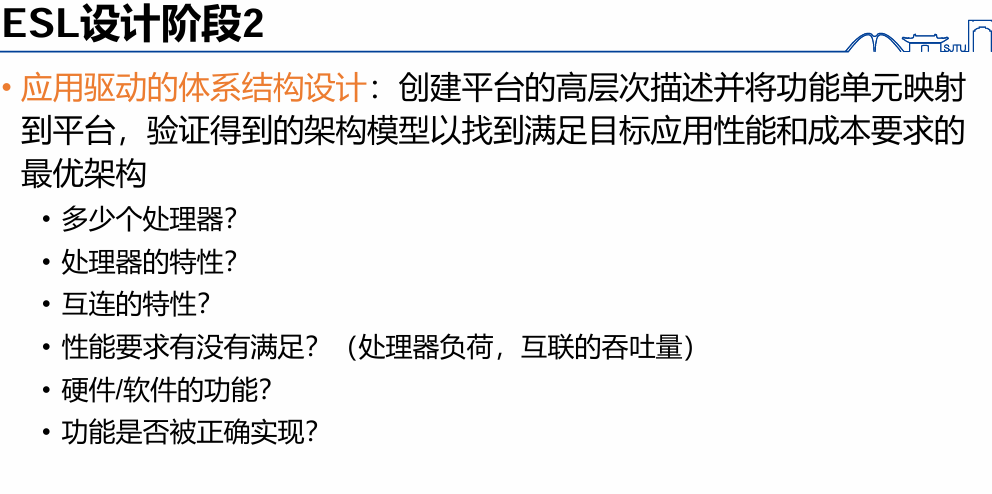

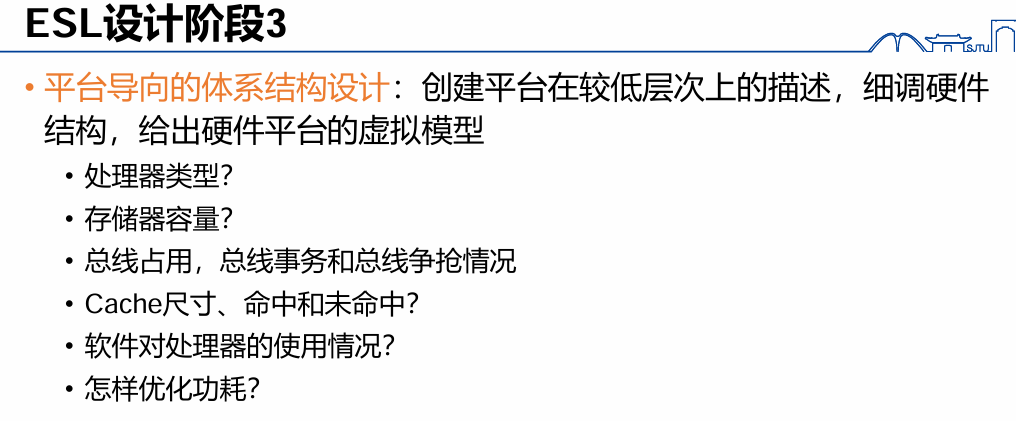

ELS设计阶段

ELS设计分为3个阶段:

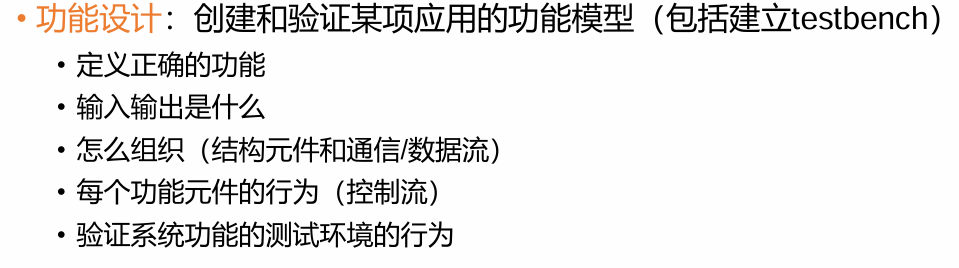

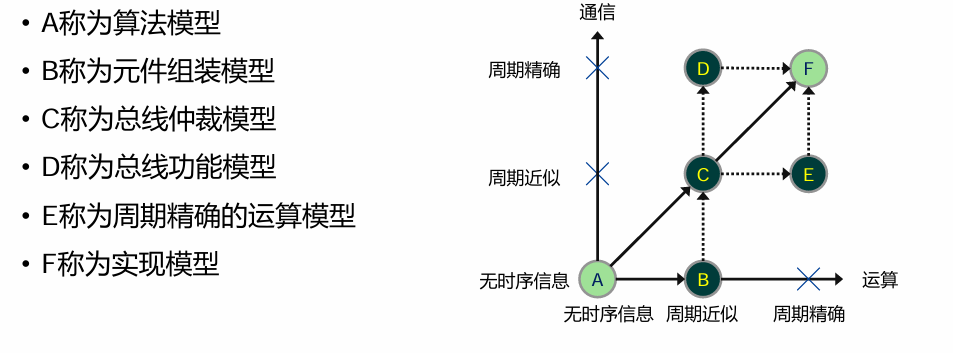

ELS设计模型

事物级建模

事务指模块之间的数据和事件的交互。数据交换可以是一个或多个字,

或者是一种数据结构。而诸如同步或者中断等则属于事件的交互

•事务级建模的核心概念是在一个系统建模过程中将运算功能和通信功

能分开,模块之间的通信通过函数调用来实现

与寄存器传输级模型相比较,事务级建模可以减少事件和信息的处理,

所需的程序代码更少,执行速度更快

• 根据实际需要提供足够的设计精度,根据描述系统精度的不同,事务

级模型可以分为三种:

• 没有时序信息的模型

• 周期近似的模型

• 周期精确的模型

ELS设计语言

业界获得较多支持和应用较为广泛的语言是SystemVerilog和SystemC

SystemVerilog是在Verilog上的扩展,吸收了C/C++中的一些特性,可以实

现和C的仿真。由于是在Verilog上的扩展,SystemVerilog的优势在于基于

时钟的建模能力和验证能力。但在TLM的抽象上还存在一些不足,如缺少

抽象的数据类型

• 更为成功的是SystemC,SystemC是OSCI推出的基于C++扩展的描述语言。

是一种可以完成电子系统从软件到硬件的全部建模过程的语言。在目前的

设计中软件开发占到设计任务的60%-90%,基于C++扩展的语言SystemC

比从HDL扩展的语言有更加有利的发展趋势。SystemC完全支持TLM建模,

而且OSCI已经提出了TLM建模的标准。而其他语言目前还没有完全支持

TLM建模。

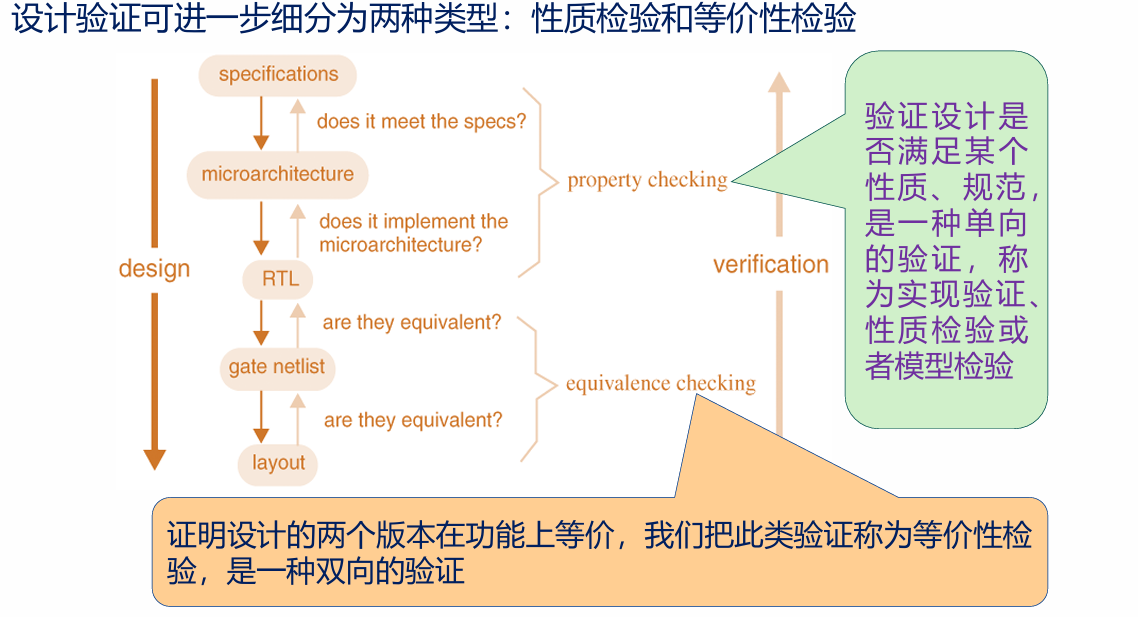

Lecture 4 SoC验证

设计验证(Verification)的目的是确认设计的功能正确性和性能(速度和功耗等)满足设计要求,贯穿于设计的整个过程。

随着系统复杂的的提高,bug的数量也在提高,而找出bug的代价更大。

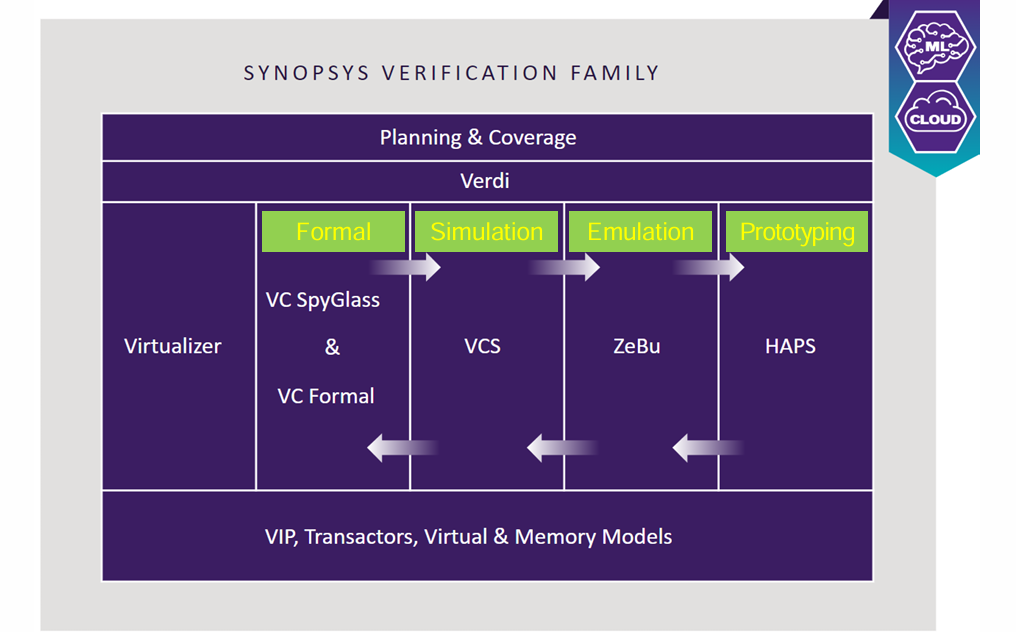

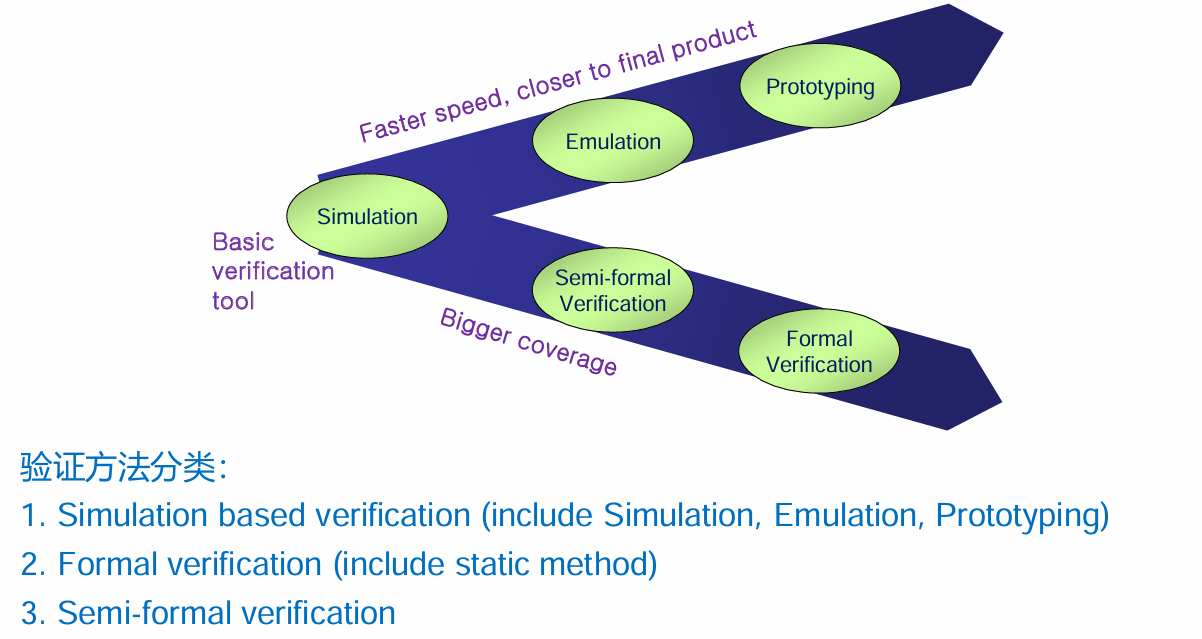

SoC验证方法学

根据验证的方式可以分为:

Formal,Simulation,Emulation,Protyping

从方式来分类可以分解基于仿真的验证和基于形式的验证2大类。

基于仿真的方法需要设置输入向量和预期结果,然后进行结果对比。

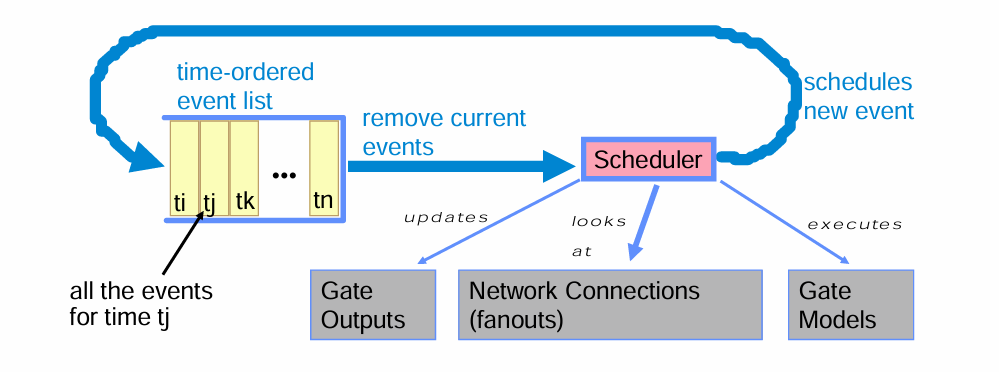

事件驱动的仿真 simulation

时间驱动的仿真,将各个时间节点发生的时间进行归类,然后以特定顺序调用,以此模拟真实的系统。

代码覆盖率和功能覆盖率

(参考SV课程中的内容)

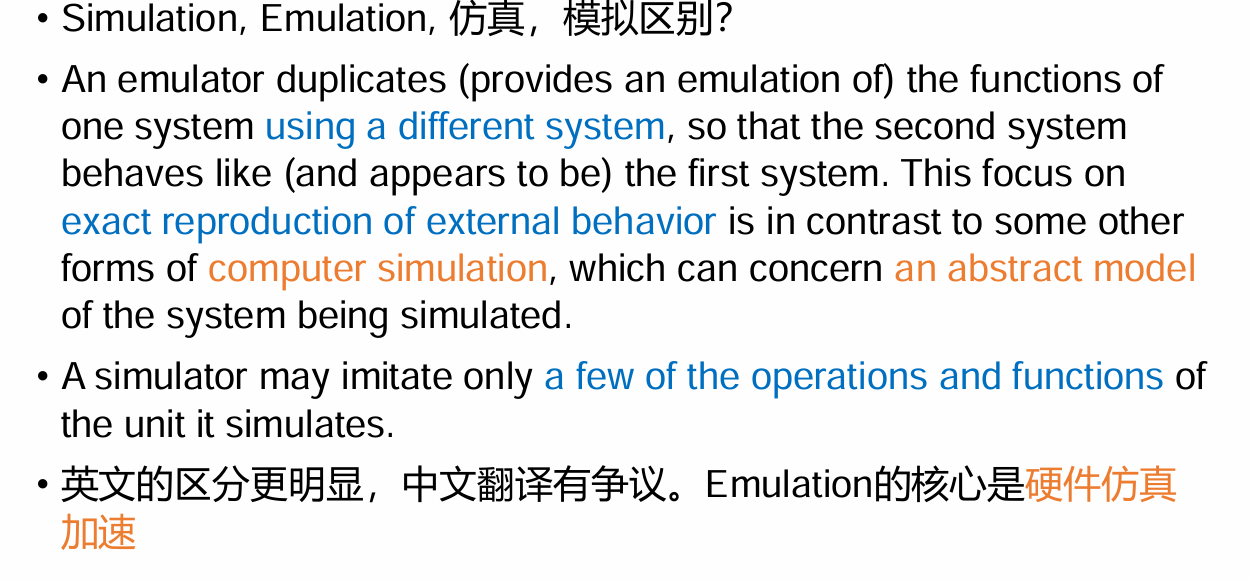

仿真simulation和模拟emulation的区别

核心在于emulation采取一套不同的硬件系统来验证功能

Emulation的问题在于成本过高。

形式化验证

可以达到100%覆盖率

仅适用于小尺寸的有限状态系统

对于类似soc这样的复杂系统,其输入空间的组合近似无穷大,如果不用形式验证的方法,很难穷尽所有的输入可能。

形式化验证的分类

主要分为模型检查和等价性检查。

其中等价性检查又分为LEC(logic equivalence)和SEC(sequential equivalence)

基于AI和深度学习的验证

测试平台搭建

SoC混合信号验证

Lecture5 逻辑综合

gtech: 与工艺无关的门级网表

逻辑综合要解决的问题

单的综合只需要将RTL读入综合软件并elaborate即可得到门级网表,但

这并不代表综合真正成功

• 对于同步逻辑电路,综合成功表示综合后的电路中,触发器等时序逻辑部

件能在正确的时间(时钟沿)得到正确的数据,即满足时序要求,同时需要满

足扇出、负载等约束

• 触发器正确读取数据的关键

• 数据在时钟沿之前稳定足够的时间,即数据不要到达太晚,应满足建立时间(setup

time)要求

• 数据在时钟沿之后稳定足够的时间,即数据不能到达太早,应满足保持时间(hold

time)要求

• 时钟沿会在正确的时刻出现,即时钟质量要满足要求

• 可简单认为综合主要是为了保证建立时间、保持时间、时钟这几项要求

Synopsys DC 综合流程

- set library

- Read design

- Defign environment

- Sent design constraints

- Select compile strategy

- Optimize the design

- Analyze and resolve design problems

- save design data

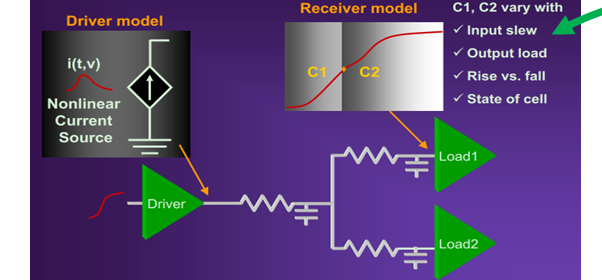

CCS 模型

CCS模型即复合电流源模型Composite Current Source,精度可达HSpice的2%以内,但CCS库尺寸比NLDM库大一个数量级。

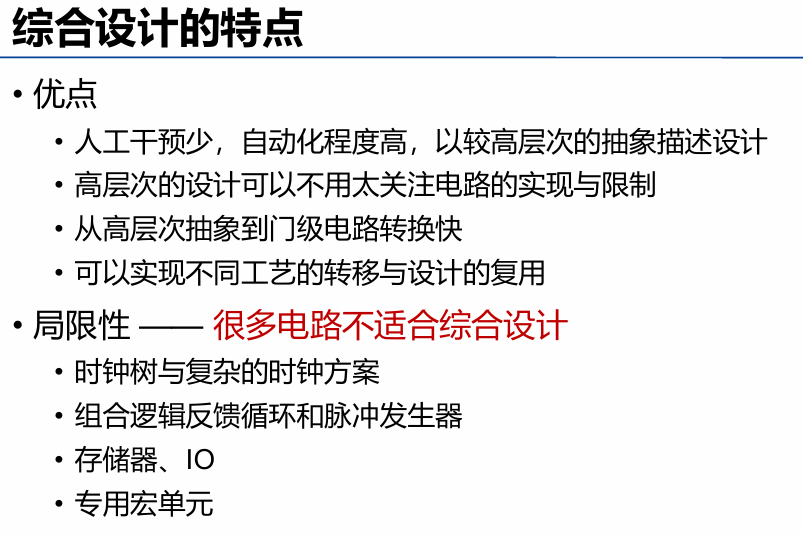

无法综合的部分

类似memory之类的模型无法由逻辑综合直接得到,而是需要专用工具或使用成型IP:

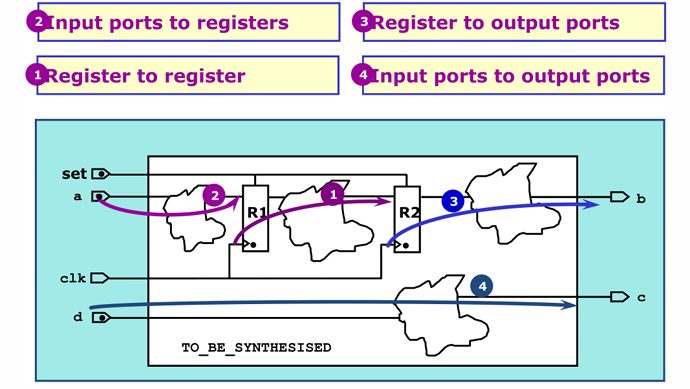

需要约束的时序路径

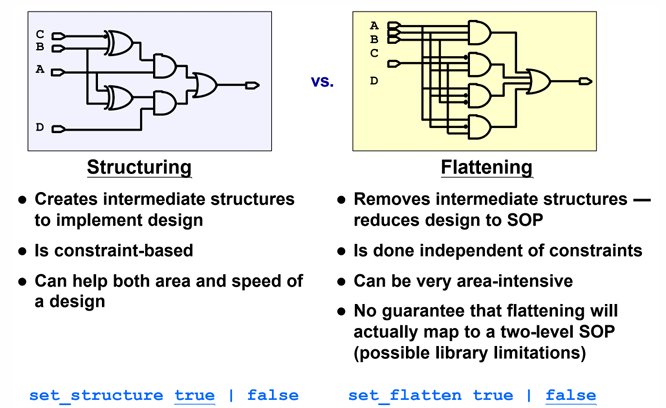

电路优化

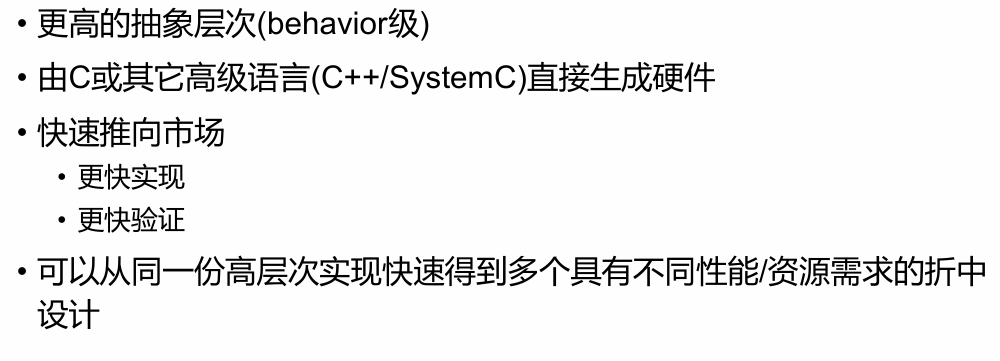

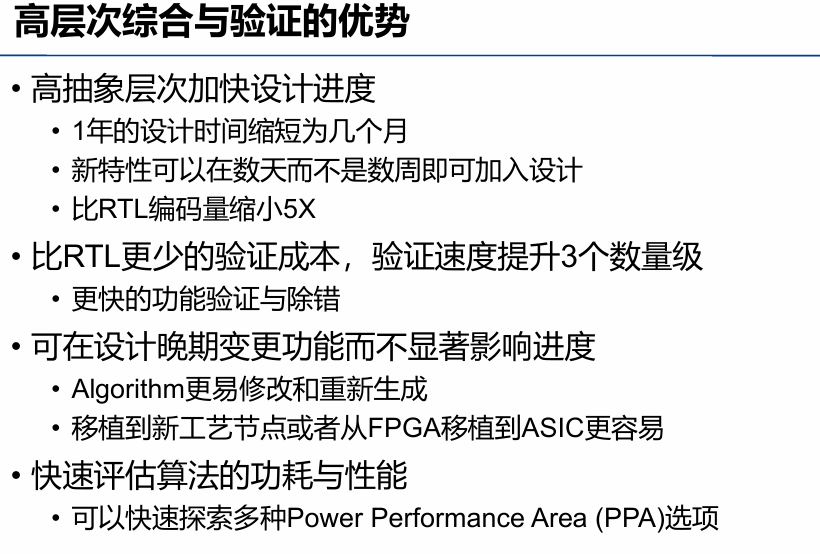

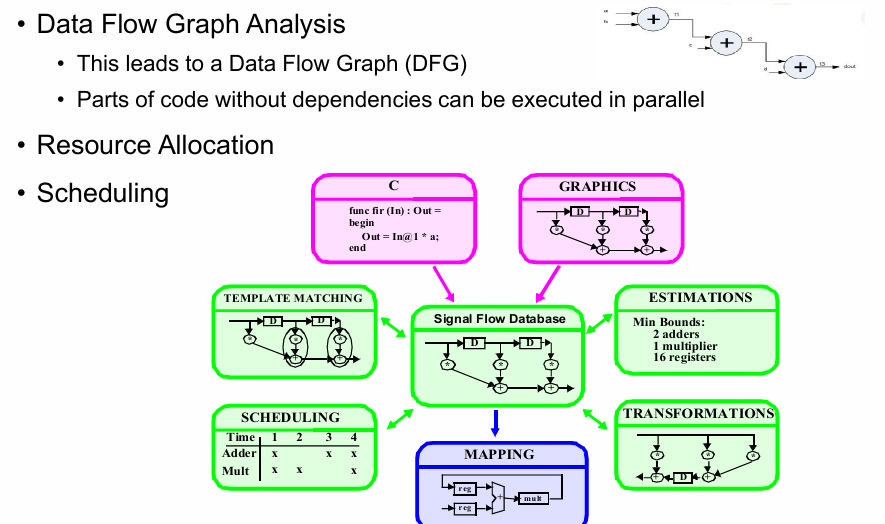

高层次综合HLS

Lecture 6 STA

建立时间和保持时间

Setup Time – 建立时间,数据在时钟沿之前必须保持稳定的时间长度

Hold Time – 保持时间,数据在时钟沿之后必须保持稳定的时间长度

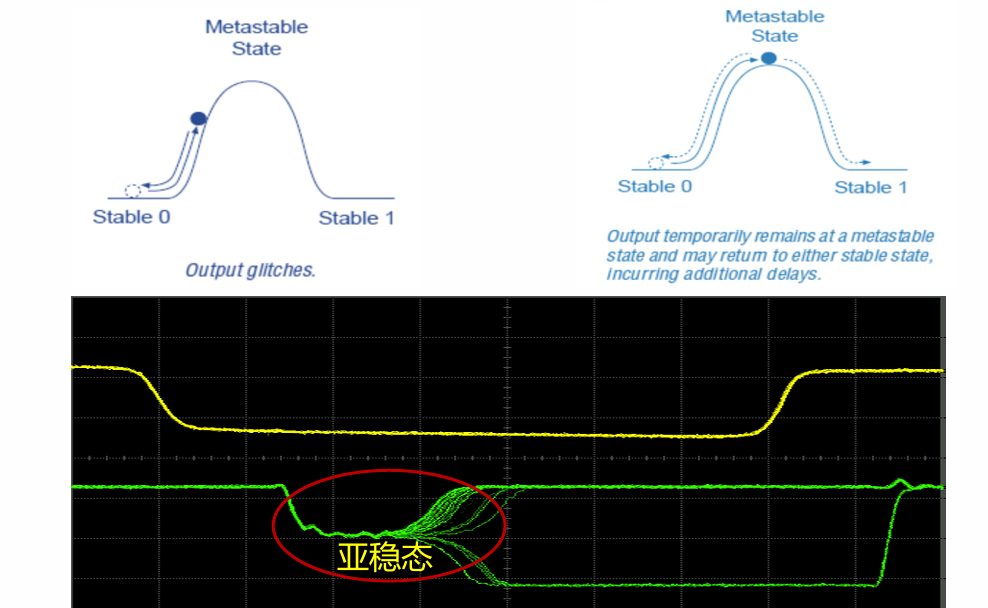

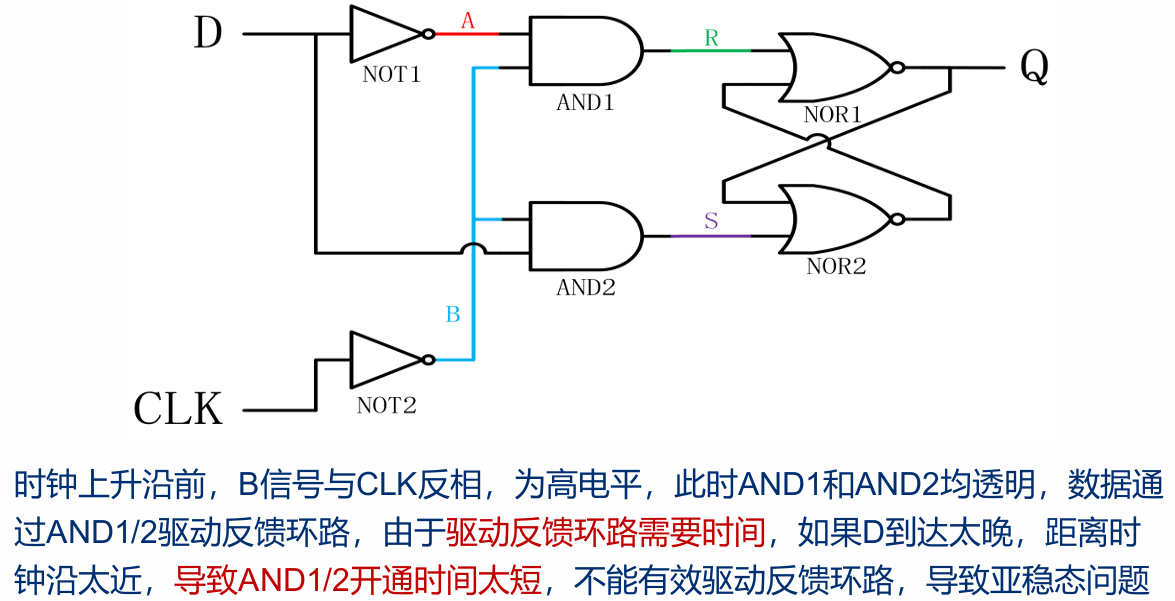

亚稳态

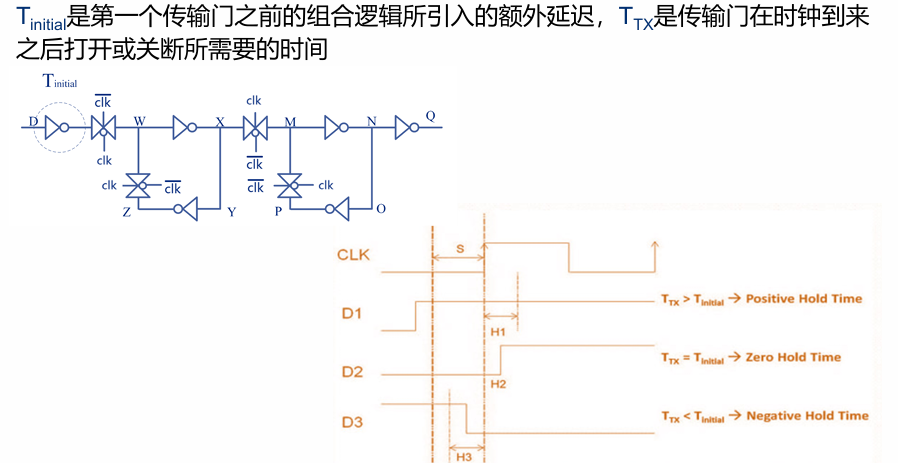

Negative hold time

建立时间总是正的,但保持时间可以为正值、零,甚至负值

• 某些触发器可能需要set-reset-enable或者scan-enable功能,或者其它

原因,使得触发器第一个传输门前存在部分组合逻辑

• 这些额外的组合逻辑会在输入数据D到第一个传输门的路径中引入额

外的延迟,此额外的延迟可能使得保持时间为正、零或者负