CH1 Introduction

1.1 About AXI

AXI 是一种支持高性能的传输协议。

协议的功能包括:

- 适用于高带宽低延迟设计

- 不需要复杂的桥接即可实现高频操作

- 可以满足多种组件的接口需求

- 适用于具有高初始访存延迟的memory controller

- 灵活的互联架构实现方式

- 向后兼容AHB和APB接口

协议的主要特性有:

- 独立的地址/控制及数据相位

- 支持使用strobes进行非对齐数据传输

- 仅使用base address进行burst传输

- 独立的数据读写通道,可以实现低成本的DMA

- 支持发送多个outstanding 地址。(outstanding指已发出但未完成的传输,见后文)

- 支持乱序传输

- 允许添加寄存器保证时序收敛

1.2 AXI Architecture

AXI协议基于事务级传输,具有以下5个独立的通道:

- Write request, 信号名以 aw开头

- Write data, 信号名以w开头

- Write response,信号名以b开头

- Read request,信号名以ar开头

- Read data,信号名以r开头

request 通道携带需要传输数据的一些控制信息(如地址,传输长度等)。一次传输被看作一次请求。

数据可以通过以下方式在Master和Slave直接进行传输:

- 通过 write data channel将data 从Master传输到slave.在一次传输事务中,Slave通过Write Respense通道通知Master传输结束。

- 通过read data channel将数据从Slave传到Master

AXI协议拥有以下功能:

- 允许地址信息先于数据信息传输

- 允许多个outstanding传输事务

- 运行传输事务无序完成

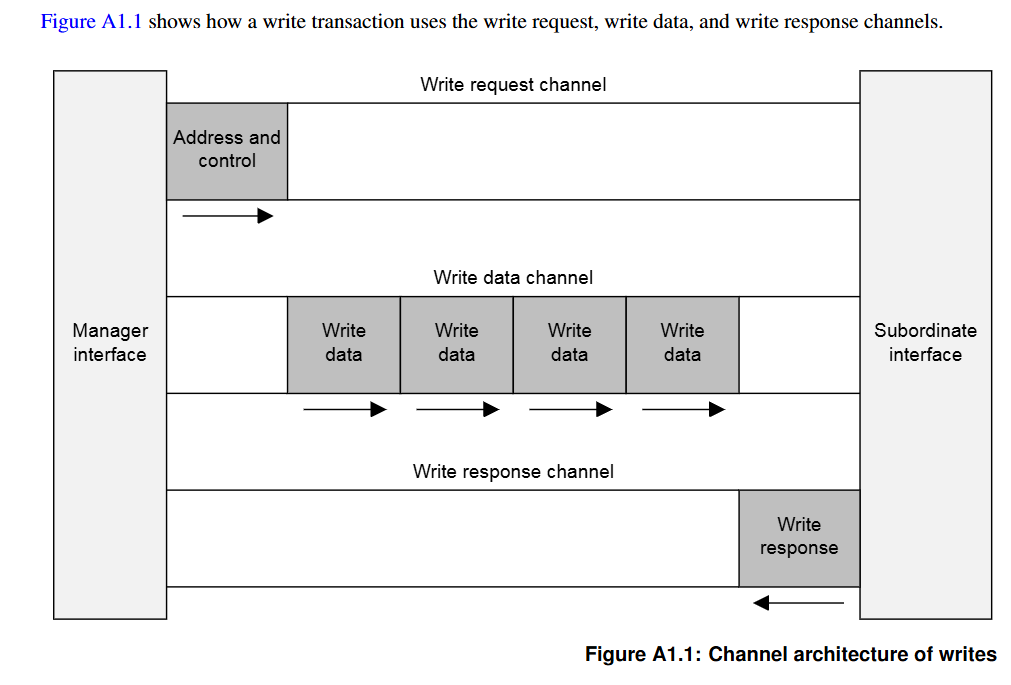

下图是一个使用write request channel,write data channel和write response channel的写传输示例。

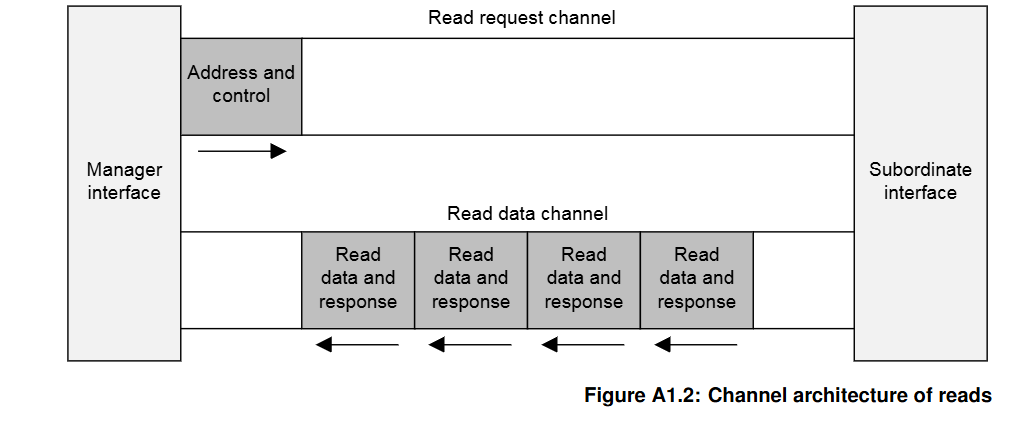

使用读通道和读请求通道的示例:

1.2.1 Channel defination

每一路通道都含有一系列信号以及valid,ready的2路握手信号。

信号源使用valid信号来指示对应通道的address,data或控制信息有效,接收方使用ready信号来指示其可以接受信息。

此外write data channel和read data channel还分别含有一个last信号来指示传输的最后一个数据。

1.2.1.1 Write and read request channels

独立的读/写请求通道,对应的通道包含传输事务需要的地址和控制信息。

1.2.1.2 Write data channel

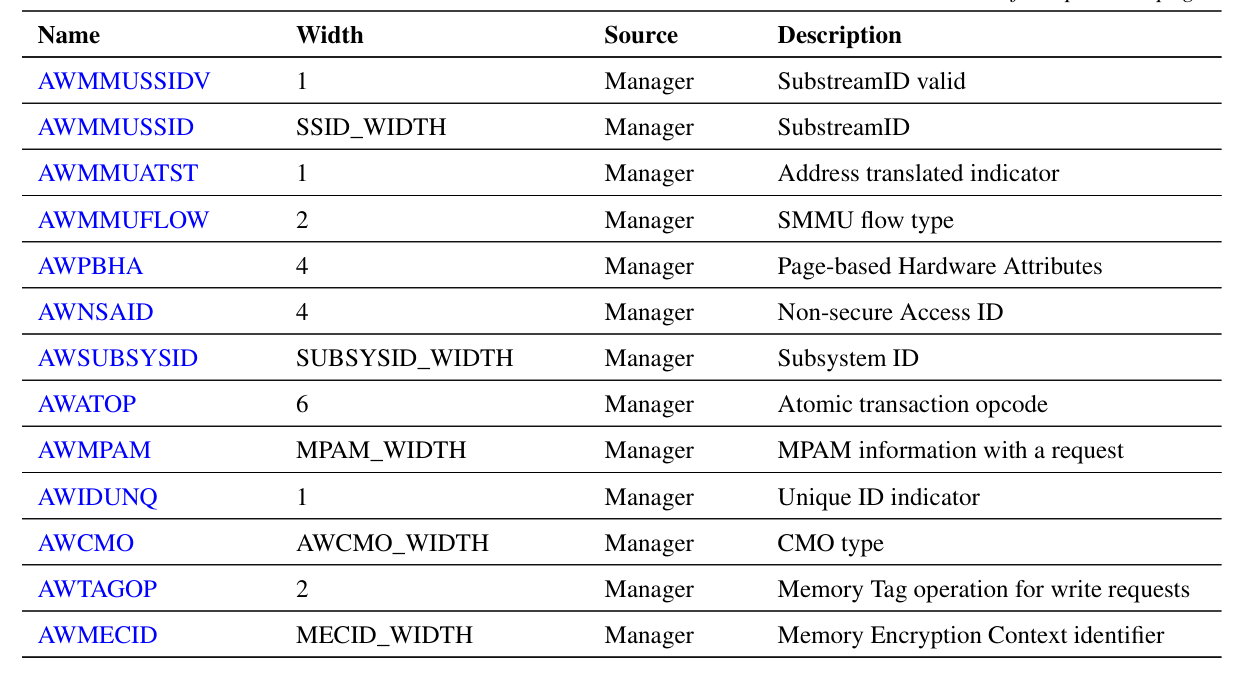

Write data channel 携带从Master写入Slave的数据,包括:

- data 信号,wdata的宽度由DATA_WIDTH指定,可以是6,16,32,64,128,256,512,1024bits.

- 字节选通信号(strobe),每位对应8bits,指示对应的byte是否有效。

写数据通道被认为是buffered的,因此Master可以在无需Slave确定数据的情况下执行写传输操作。

1.2.1.3Write response channel

Slave 通过 写响应通道来响应写传输事务。所有的写传输都需要在写响应通道上发送完成信号。

但如图a1.1所示,仅针对传输完成的事务发出响应信号,而不是响应事务中的每个数据。

1.2.1.4 Read data channel

read data channel既包含读数据,也包含读响应信息,包括:

- 读数据rdata,宽度由DATA_WIDTH指定,可以是6,16,32,64,128,256,512,1024bits.

- 读响应信号,指示读传输操作的完成。

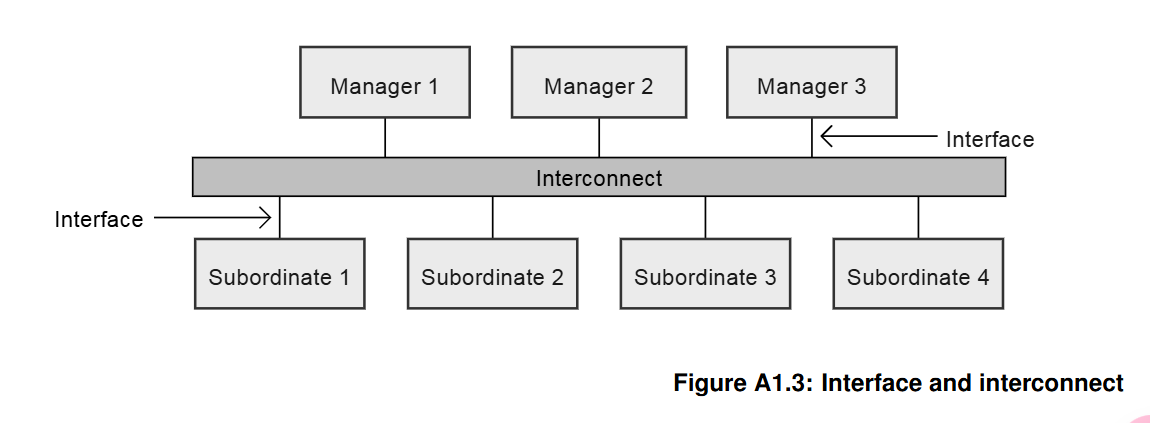

1.2.2 Interface and interconnect

一个典型的多主多从系统的架构如下:

AXI协议为以下接口之间的连接提供单一接口定义:

- Manager和Interconnect之间

- Subordinate和Interconnect之间

- Manager和Interconnect之间

1.2.2.1 Typical system topologies

大多数系统使用如下的拓扑结构:

- 共享的request和data channel

- 共享的request channel和多个data channel

- 多层,具有多个request和data channel

大多数系统中,请求通道带宽要求明显低于数据通道带宽要求。此类系统可以通过使用具有多个数据通道的共享请求通道来实现并行数据传输,从而在系统性能和互连复杂性之间实现良好的平衡。

1.2.3 Rigister slices

每个AXI通道传输的信息是单向的,并且架构并不要求每个通道之间具有固定的关系,这种性质意味着,可以以一个额外时钟周期为延时的代价,在channel的任何节点插入寄存器。并使以下操作成为可能:

- 在时钟周期延迟和频率之间进行trade-off

- 处理器和高性能memory(一般是cache或sram)之间的直连。同时使用简单的寄存器切分,隔离掉与性能不太重要的外设接口之间的较长路径。

1.3 Terminology

注意区分transfer和transaction,前者是一次单周期的传输,后者是一次完整的传输事务,一个transaction包含一个或多个transfer。

CH2 Signal list

本章介绍AXI协议的信号列表,其中一些信号是可选的,并不是所有接口中都包含它们。

2.1 Write Channel

2.1.1 Write request channel

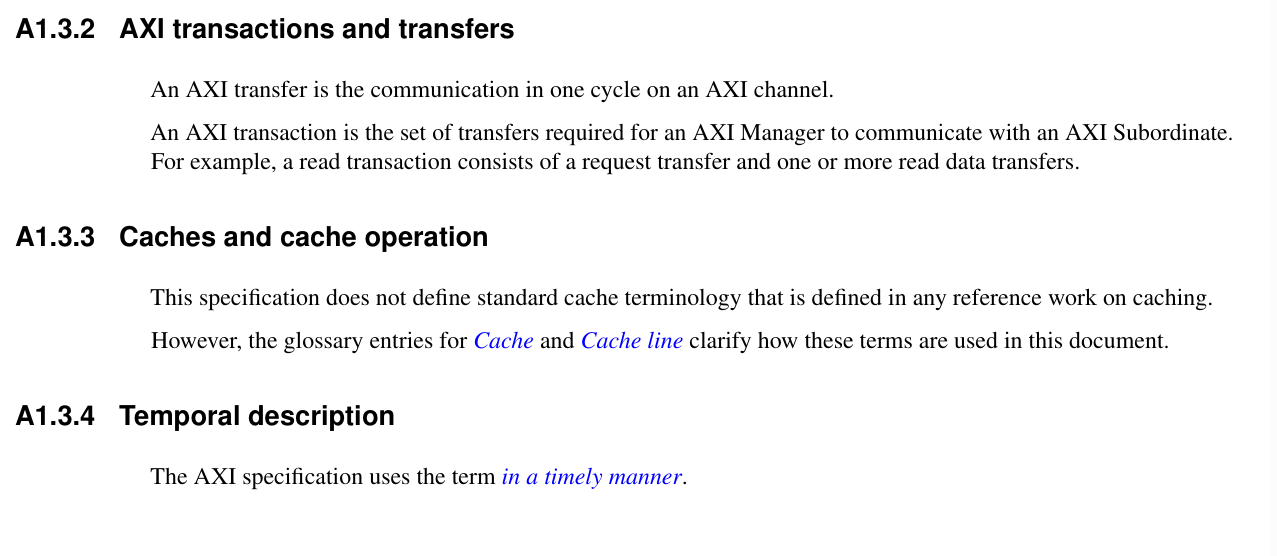

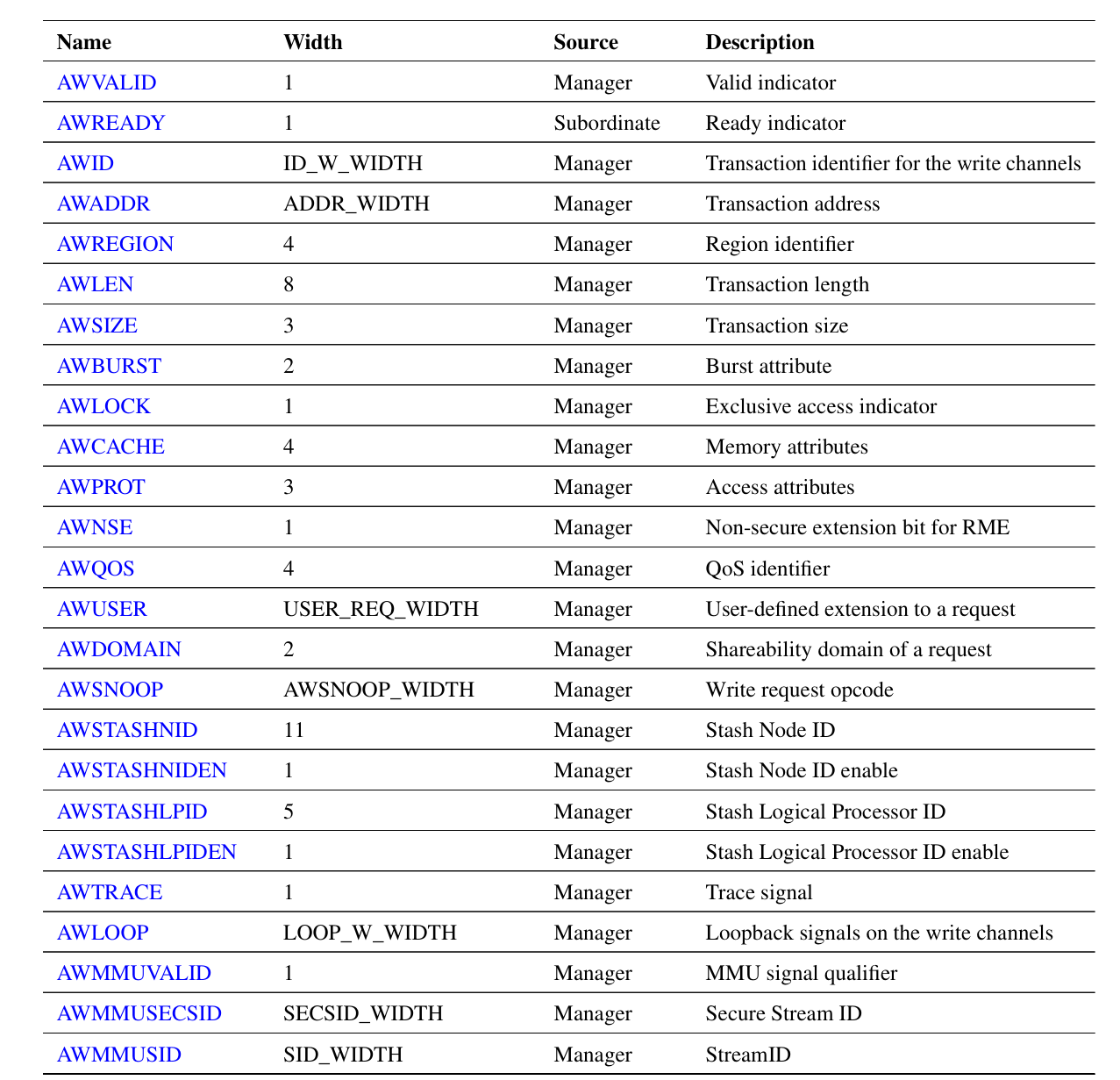

Write reques channel包含以下信号:

这个channel中的信号均以aw开头。

2.1.2 Write channel

write channel的信号以w开头

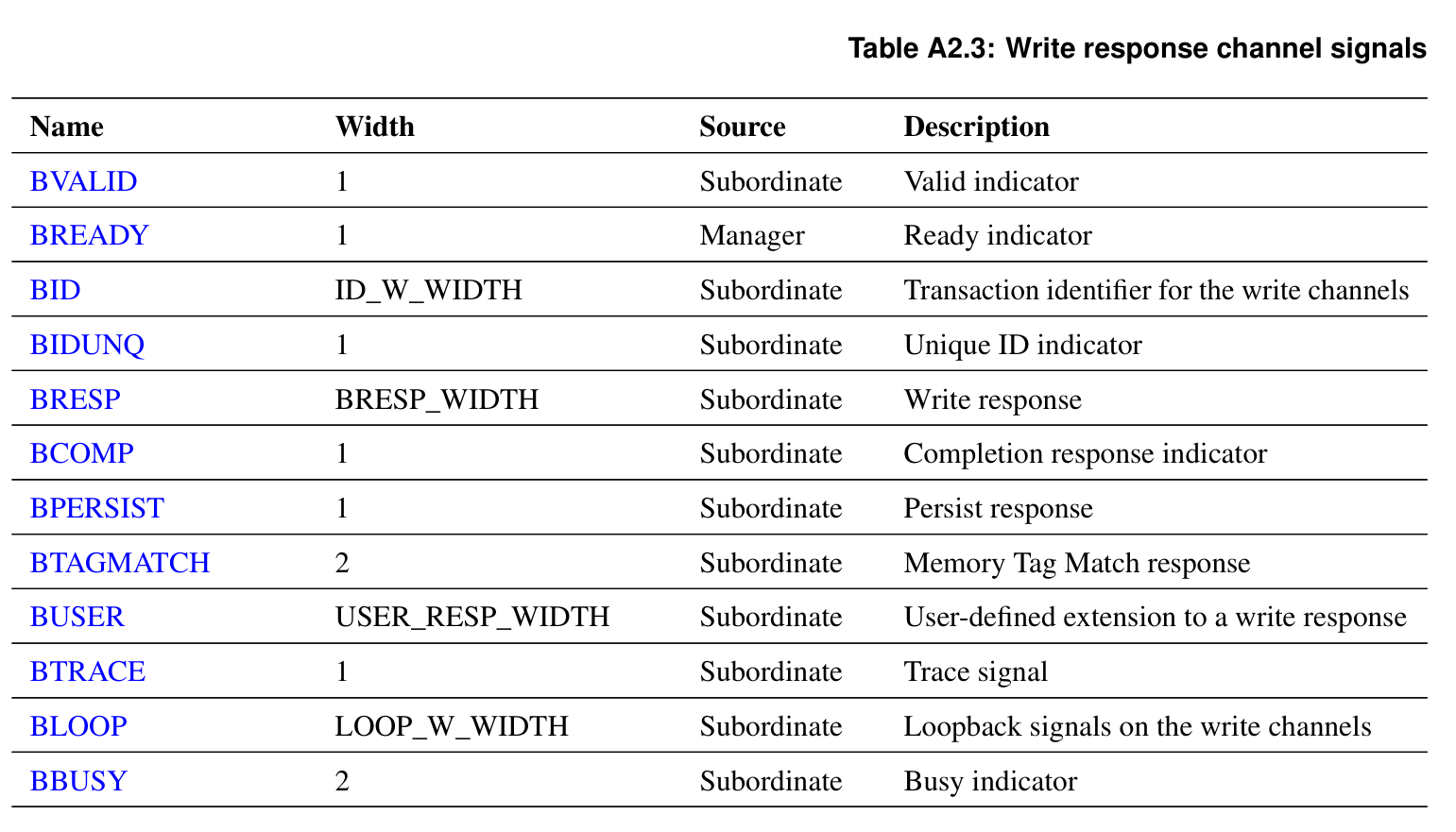

2.1.3 Write respense channel

write resopnse channel的信号以B开头。

2.2 Read channel

Read channel用来传输读请求,读数据,读响应,以及对应的内存一致性操作和DVM(Distributed Virtual Memory)信息。

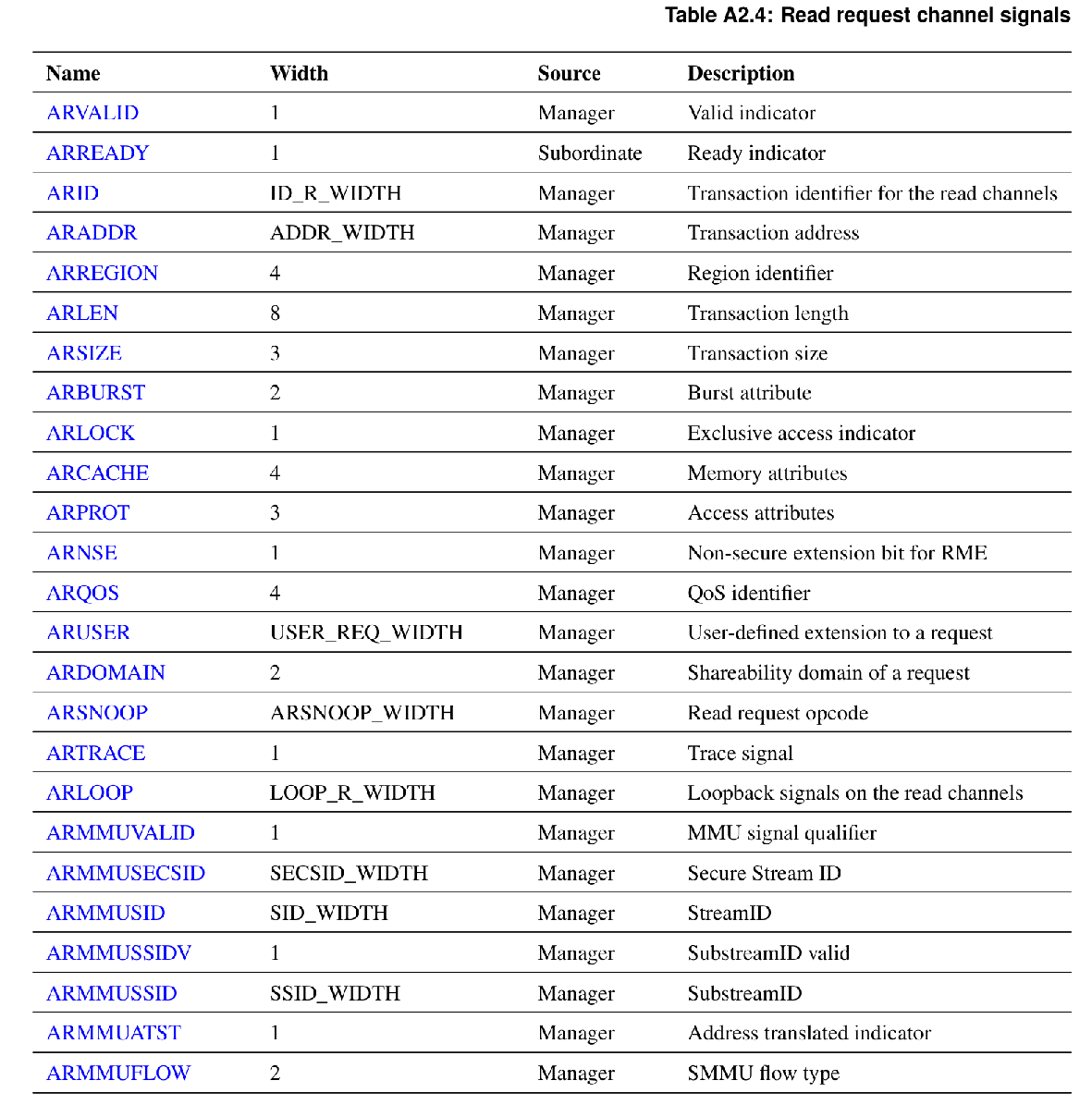

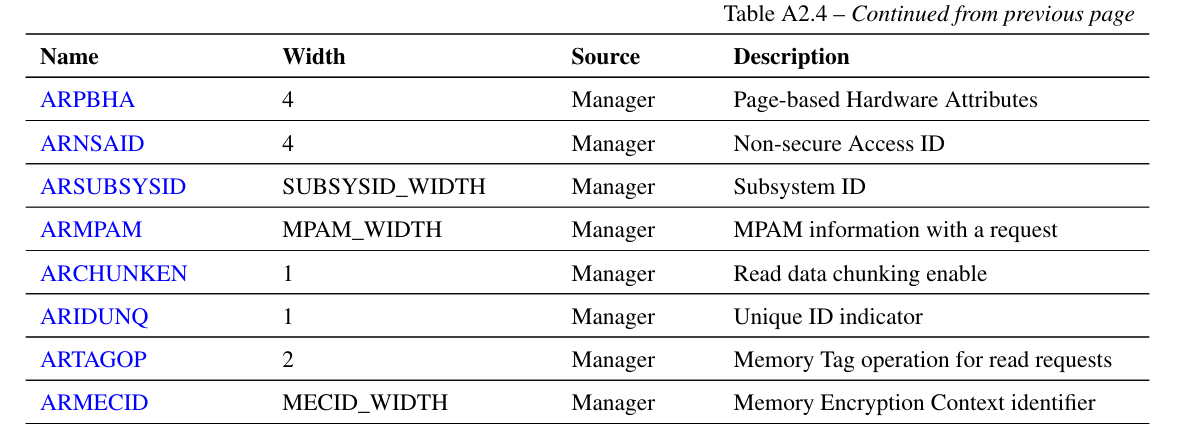

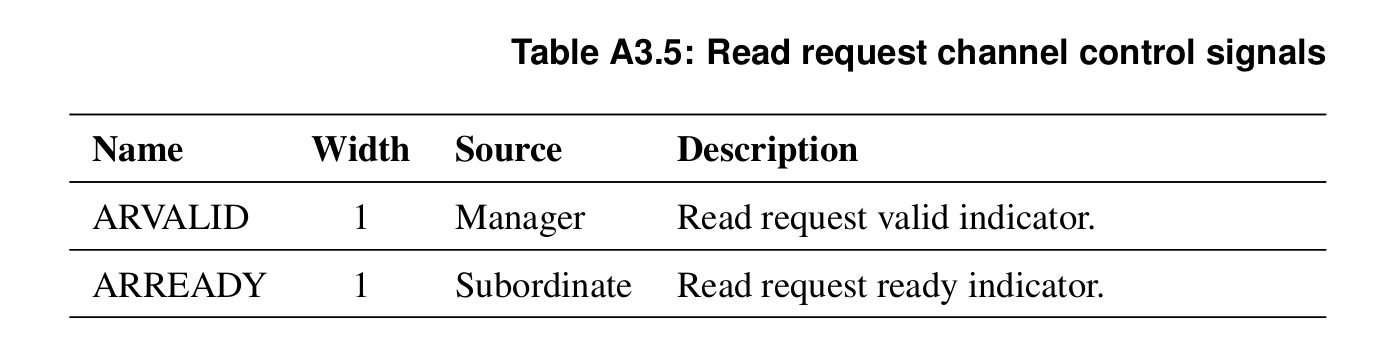

2.2.1 Read request Channel

read request channel的信号以ar开头

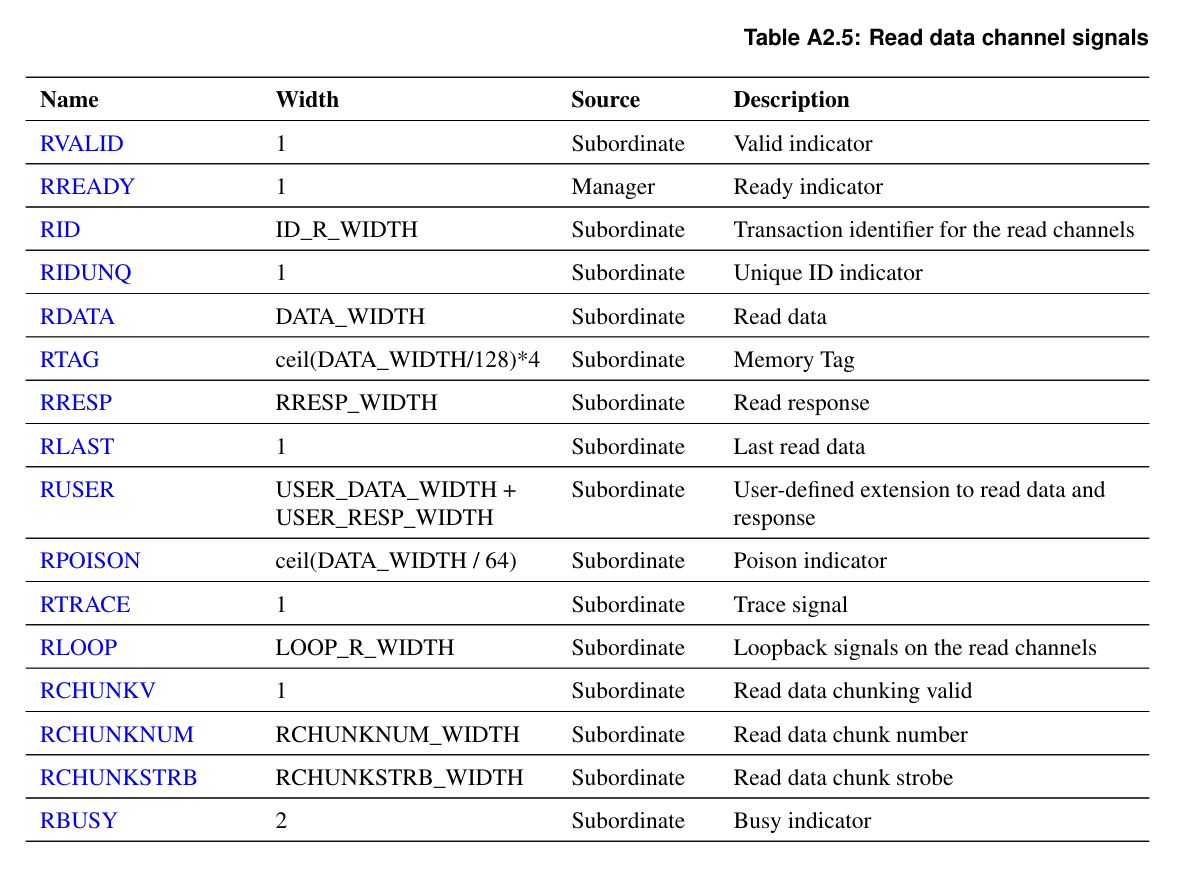

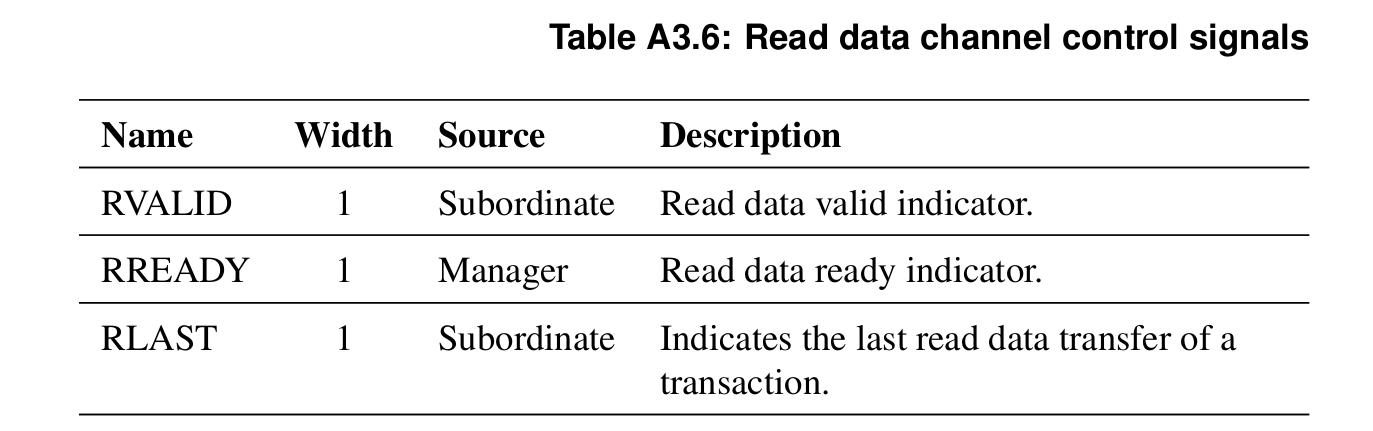

2.2.2 Read channel

read channel 的信号以r开头。

2.3 Snoop channel

本协议中,Snoop channel只用来传递DVM信息。

2.3.1 Snoop request channel

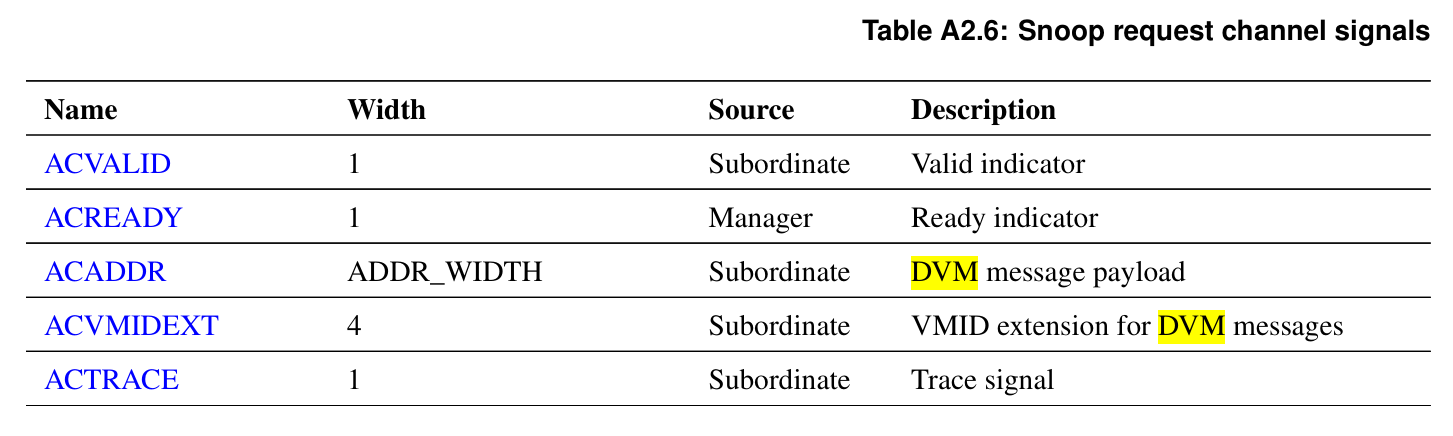

snoop request channel包含以下信号,信号名以ac开头:

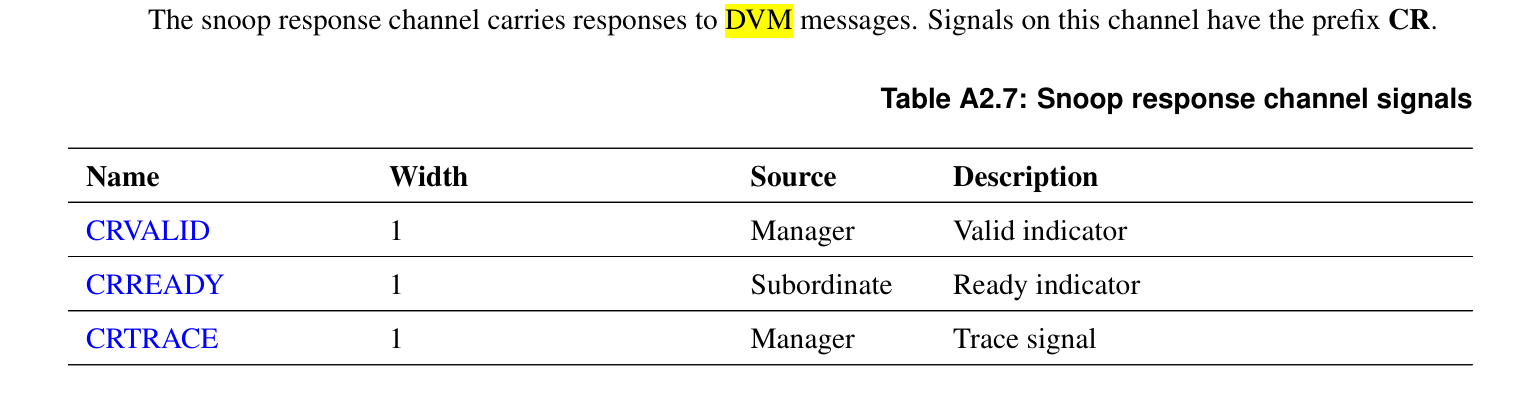

2.3.2 Snoop resopnse channel

Snoop response channel 信号以cr开头。

2.4 Interface Level Signals

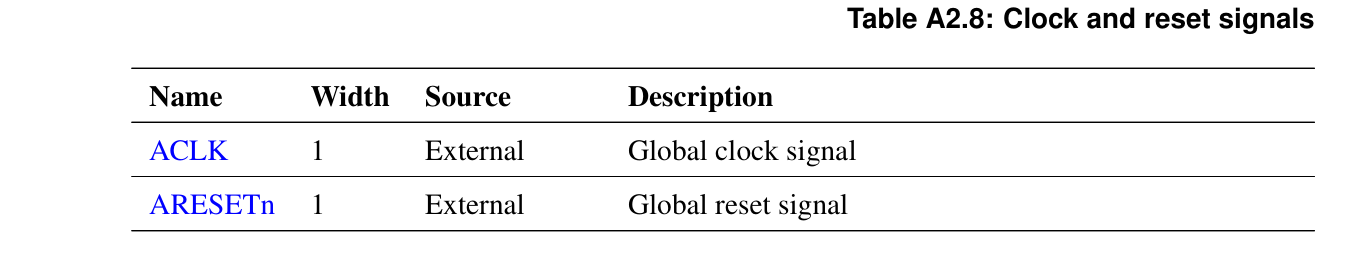

2.4.1 clock and reset signals

所有的信号采用一个全局的同步时钟和一个异步的复位信号:

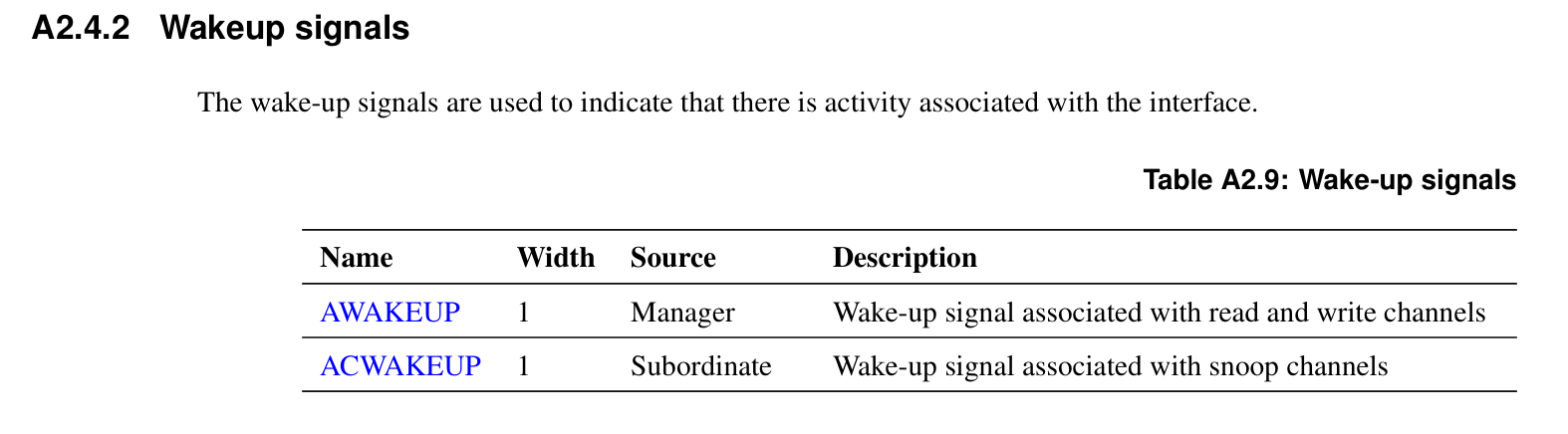

2.4.2 Weakup signals

Weakup 信号用来指示端口有活动的信号。

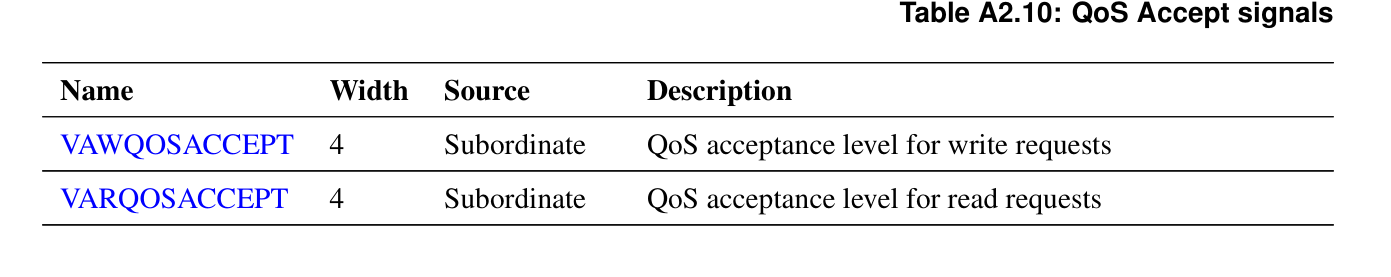

2.4.3 QoS(Quality of Service) Accept signals

QoS Accept signals can be used by a Subordinate interface to indicate the minimum QoS value of requests that it

accepts

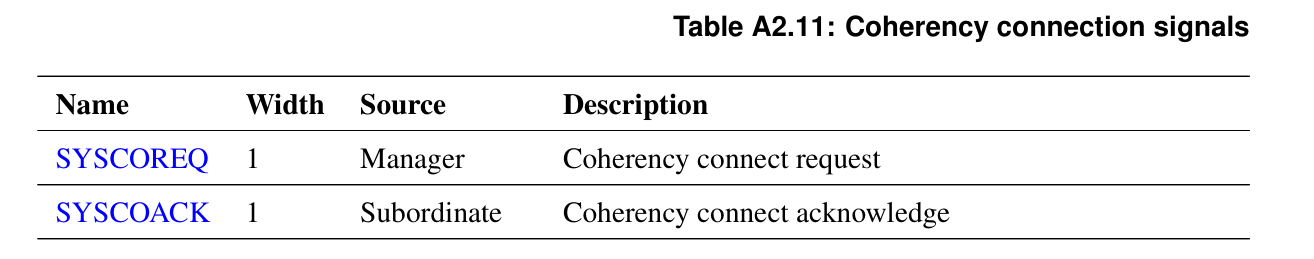

2.4.4 Coherency Connection signals

The coherency connection signals are used by a Manager to control whether it receives DVM messages on the AC

channel.

2.4.5 Interface control signals

The interface control signals are static inputs to a Manager interface that can be used to configure interface

behavior.

CH3 AXI Transport

3.1 Clock and reset

3.1.1 Clock

AXI 接口采用一个时钟信号,ACLK,所有的输入信号在ACLK的上升沿采样,所有的输出信号在的变化也发生在ACLK的上升沿之后。

在Master和Slave 接口中,输入和输出之间不能存在直接的组合逻辑路径。

3.1.2 Reset

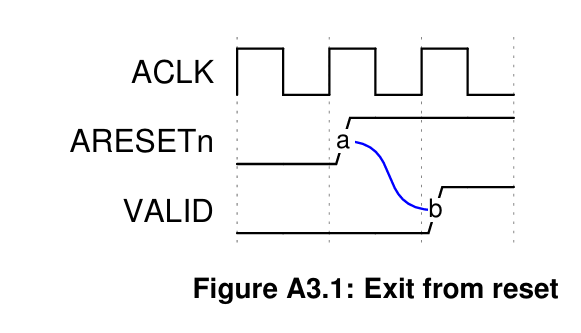

AXI协议采用一个下降沿有效的复位信号,ARESETn,复位信号可以被异步复位,但是只能在clk的上升沿同步释放。

复位期间需执行以下操作:

- Master 拉低awvalid,wvalid和arvalid信号

- Slave拉低 bvalid,rvalid信号

- 其他信号的值可以是任意值

Master可以拉高valid信号的最早时间节点是ARESETn拉高后的第一个ACLK上升沿,如下图:

3.2 Channel handshake

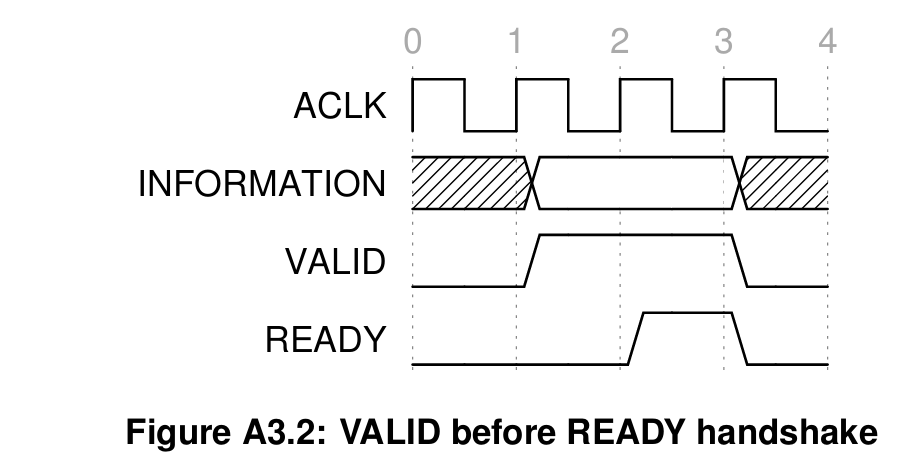

所有的axi通道都采用相同的valid/ready握手机制来完成数据,地址及控制信息的传输。

这种2路的流控制机制意味着Master和Slave双方都可以控制它们之间的数据流通速度。

信号源通过拉高valid信号来指示有可用的data,address和control information。信号的目的方通过拉高ready来指示数据可以被接受。

只有在valid和ready均为高是,传输才会发生。Master 和Slave的输入和输出端口之间一定不能含有纯组合逻辑的通路。

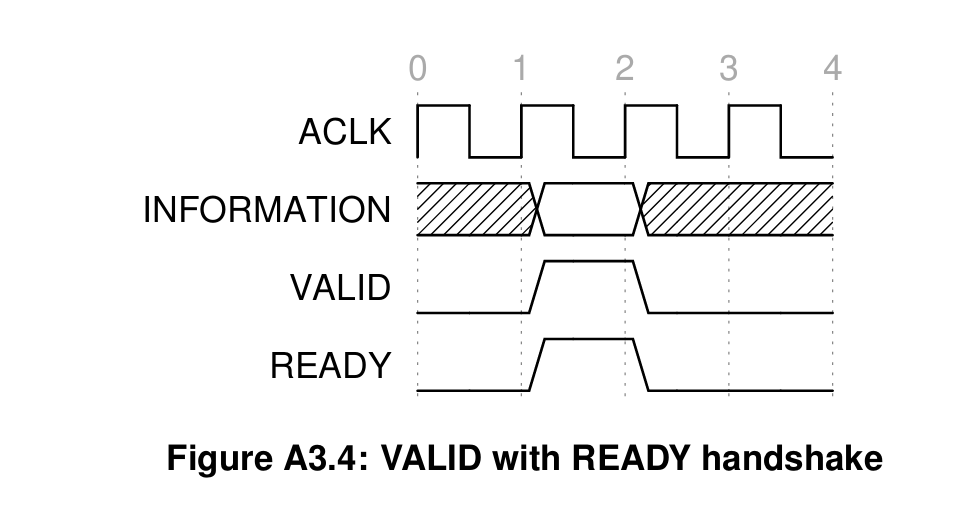

下图展现了一个握手过程:

在ready信号拉高之前,源不可以等待ready信号拉高再拉高valid。

当valid拉高,必须持续到握手发生之后,下一个valid&ready均为高的时钟上升沿。

接受方可以等待valid拉高后再拉高相应的ready。

如果ready被拉高,它可以再valid拉高之前被重新拉低.

上图中,第一个时钟上升沿后,valid&ready均拉高,在这种情况下,传输在第一个valid&ready均为高的时钟沿完成。

3.3 Write and read channel

3.3.1 Write Request channel (AW)

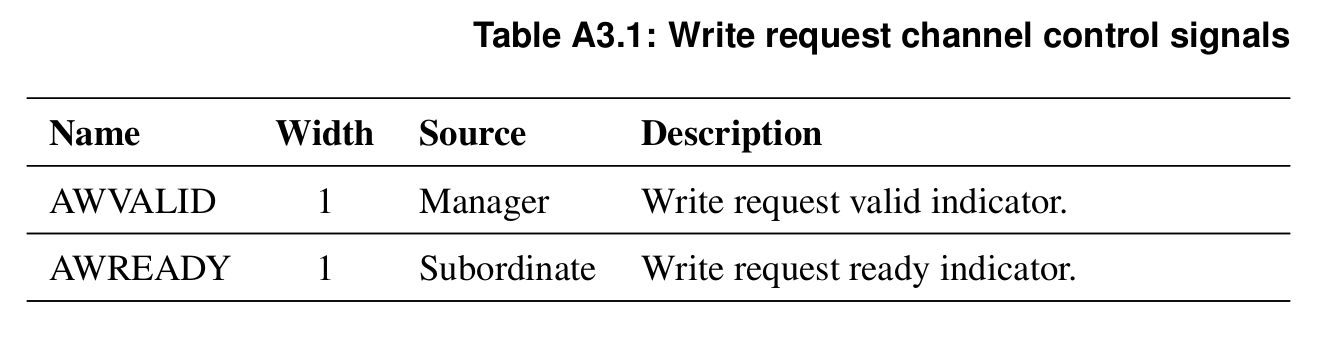

aw 通道的控制信号如下:

当且仅当发出一个有效的写请求时,Master拉高awvalid,拉高后,必须等待握手完成,及下一个awready拉高后的时钟上升沿后才可以释放。

awready的默认值可以是high或Low,推荐用high。当为high时,代表slave可以接受一个有效请求。

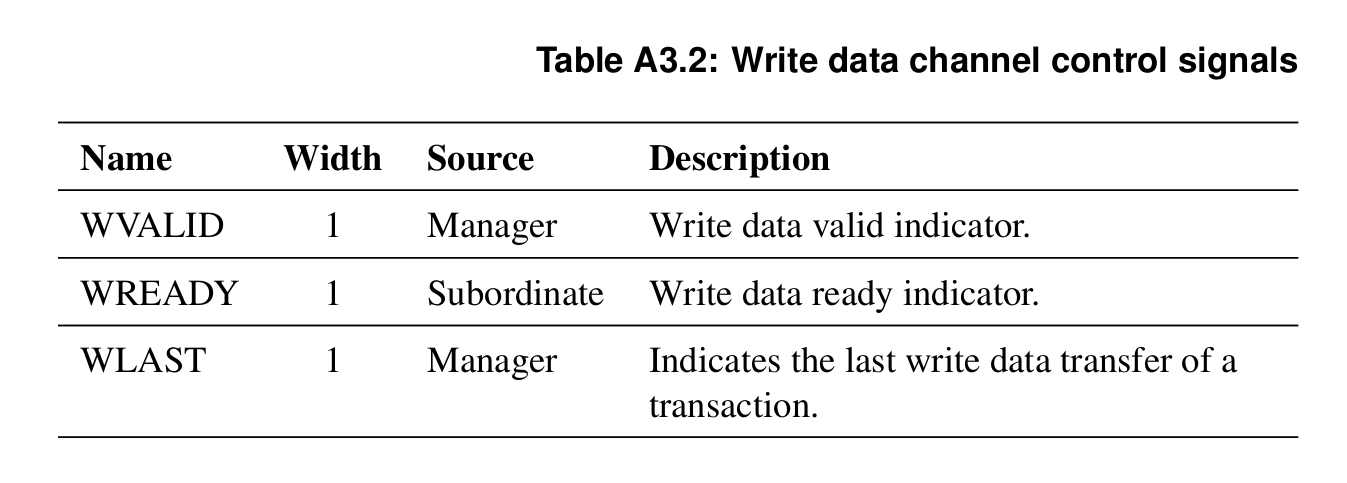

3.3.2 Write data channel (W)

在一次写事务(transaction)中,master仅当传输的data有效时拉高valid,valid拉高后,必须等待握手完成。

Master必须在一个transaction的最后一个transfer时拉高wlast信号。推荐将inactive的byte lanes上的WDATA设为0.

一个不含有wlast信号的slave接口可以忽略wlast信号。

3.3.3 Write response channel (B)

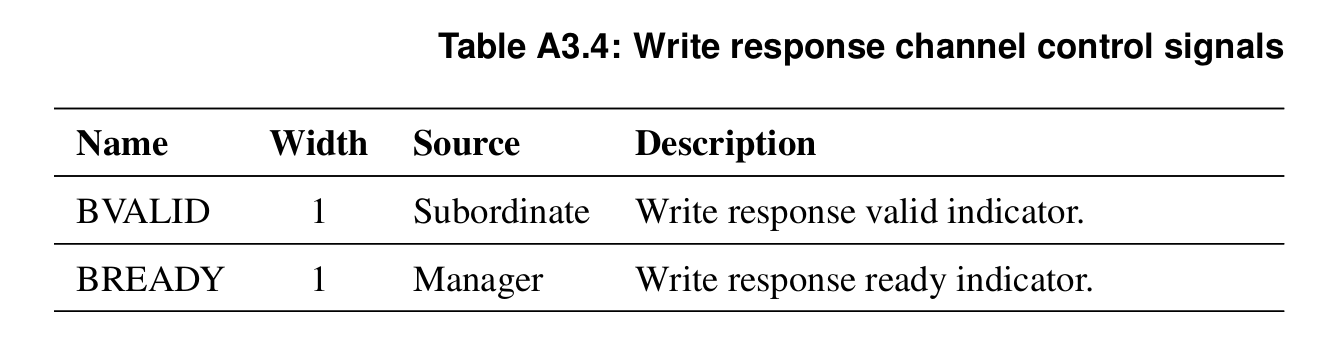

write resopnse channel的控制信号如下:

bvalid由slave发出,当且仅当发出一个有效的写相应时,将其拉高。bready的默认值可以为高,但必须是master能够接受写响应时。

3.3.4 Read request channel(AR)

和前面类似。

The Manager can assert the ARVALID signal only when it drives a valid request. When asserted, ARVALID

must remain asserted until the rising clock edge after the Subordinate asserts the ARREADY signal.

The default state of ARREADY can be either HIGH or LOW. It is recommended to use HIGH as the default state

for ARREADY. If ARREADYis HIGH, then the Subordinate must be able to accept any valid request that is

presented to it

It is not recommended to default ARREADY LOW because it forces the transfer to take at least two cycles, one to

assert ARVALID and another to assert ARREADY.

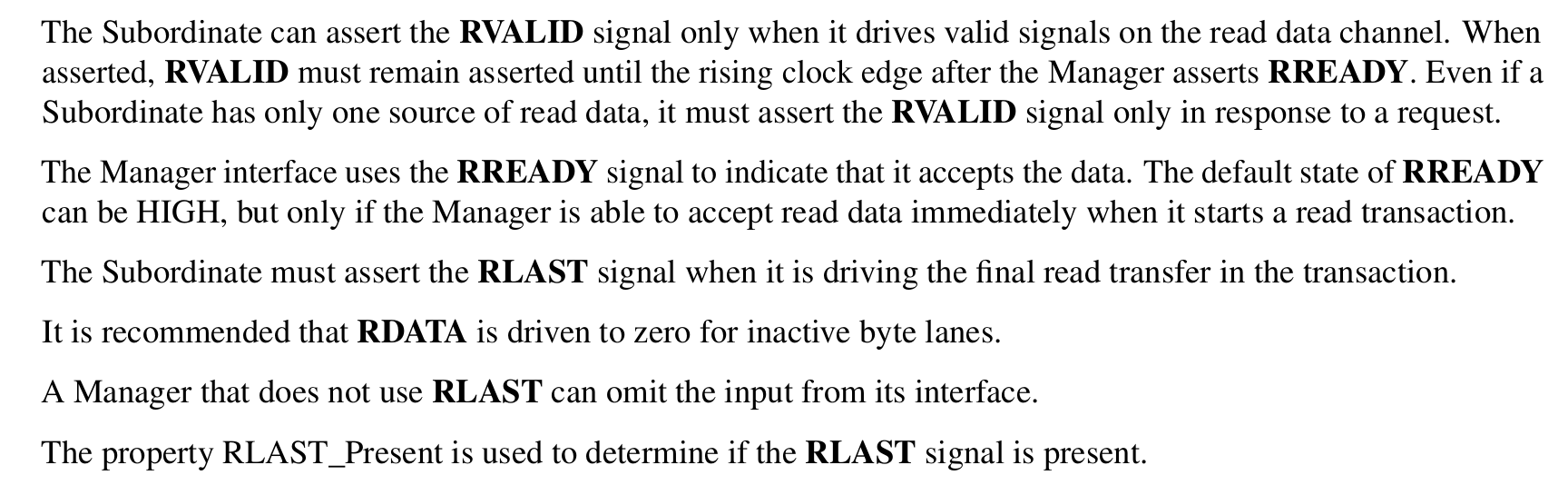

3.3.5 Read data channel (R)

read data channel 的控制信号有3个,相当于结合了write request 和write。

3.4 Relationships between the channels

AXI 协议要求维护以下关系:

- 在一个写事务的最后一个写传输之后,必须跟随一个写响应

- 写数据和写响应必须跟随在写请求之后

- 通道握手必须保证A3.5节定义的独立性(后面回介绍)

- 当Master发出写请求时,其必须已经准备好了该次事务所需所有的写数据,并且与其他的事务无关(不相干)

- 当Master发送了写请求和所有的写数据,它必须能够接收该次事务的写响应,并且与其他的传输事务无关。

- 当Master发送了一次读请求,它必须已经准备好了接收该事务的所有数据,且与其他传输事务无关。

- 注意,对使用同一ID的事务来说,Master可能依赖于返回数据的顺序,而对于ID不同的事务来说,Master只需要为读数据准备好足够的存储空间。

- Master可以等待一次传输事务完成之后,再发起下一次传输。

- Slave被允许等待一次传输事务结束之后再接受或发起下一次传输。

- 对于slave,不能因为存在leading write data的事务而阻塞那些无数据的写请求。

(协议的上述要求十分重要,不遵守时可能带来死锁或活锁)

除此之外,协议并不定义通道之间的其他关系。

这种关系的缺失意味着,例如,写数据可以在传输事务的写请求之前到达。这种情况在写请求通道拥有比写数据通道更长的寄存器(流水线)级数时就可能发生。

类似的,写数据也有可以与写请求同时到达。

当互联结构或slave模块需要确定写入地址或对应的salve接口时,它必须重新对齐请求与数据。这种重新对齐需要保证写入数据只对目标的写入slave有效。

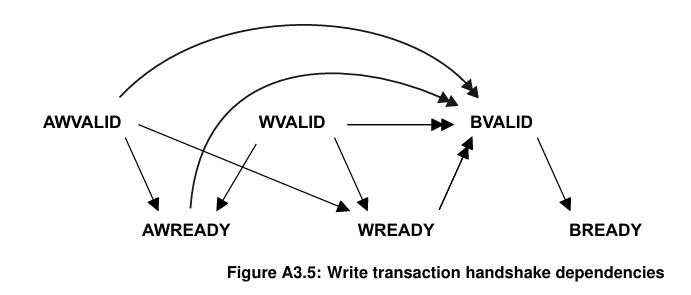

3.5 Dependencies between channel handshake signals

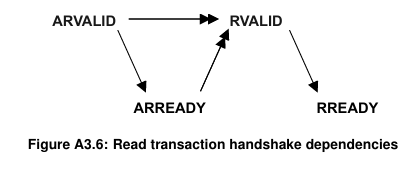

在读,写和监听事务之间存在依赖关系,这些依赖关系被以下图表所描述:

- 单箭头指向可以在箭头前的信号之前或之后断言(拉高)的信号

- 双箭头指向必须在箭头前的信号断言(拉高)之后才可以断言的信号。

3.5.1 Write transaction dependencies

写事务的依赖关系如图,具体的依赖规则如下:

- Master一定不能等slave的ready的AWREADY和WREADY,拉高后再拉高AWVALID和WVALID。对每一笔写数据事务来说都是如此。

- 在拉高AWREADY前,slave可以等待AWVALID和WVALID,或者两者都等。

- Slave可以在AWVALID和/或WVALID拉高之前拉高AWREADY

- 在拉高WREADY之前,slave可以等待AWVALID和/或WVALID

- Slave可以在AWVALID和/或WVALID拉高之前拉高WREADY

- Slave必须在 AWVALID, AWREADY, WVALID, and WREADY都拉高后,再拉高BVALID

- Slave必须等待WLAST拉高再拉高BVALID,这是因为写响应BRESP必须等写事务的最后一笔数据完成之后再开始。

- Slave必须不能等BREADY拉高后再拉高BVALID

- Master可以等BVALID拉高后再拉高BREADY

- Master可以在BVALID拉高之前拉高BREADY

3.5.2 Read transaction dependencies

对于读事务,其依赖关系如下图:

- Master一定不能等Slave拉高ARREADY后再拉高ARVALID

- Slave可以等Slave拉高ARVALID后再拉高ARREADY

- Slave可以等ARVALID拉高前再拉高VRREADY

- Slave必须等待ARVALID和ARREADY都拉高之后再拉高RVALID来指示信号有效

- Slave不能等Master拉高RREADY之后再拉高RVALID

- Master可以等RVALID拉高后再拉高RREADY

- Master可以在RVALID拉高前再拉高RREADY

Snoop channels

后面补

CH4 AXI Transaction

AXI协议使用事务级传输在Master和Slave之间进行通信,所有的传输都包括一个request和一个response.读和写事务可以包含一笔或多笔传输。

4.1 Transaction request

AXI Master通过对Slave发送一个请求来初始化一笔传输。一笔请求包括属性和第一个数据的地址。如果一笔事务包含超过一个数据传输,Slave必须负责计算之后的传输地址。

一笔传输事务不能超出4KB的地址边界。这防止了一笔传输事务跨过2个Slave的边界,同时也限制了Slave支持的地址递增数量。

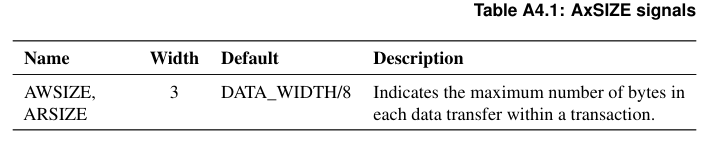

4.1.1 Size attribute

size指示了每个transfer的中数据的最大字节数。

对于读事务,size指示了每个 data transfer中必须有效的byte数

对于写事务,size指示了有多少data byte lane是active的,write strobes指示了这些byte中具体哪些是valid的。

size大小不得超过接口的数据宽度,由 DATA_WIDTH 属性确定。

如果 Size 小于 DATA_WIDTH,则每个传输使用字节通道的一部分。

在读请求通道和写请求通道中,size被AWSIZE和ARSIZE确定,本spec中,AxSIZE表示AWSIZE和ARSIZE.

可以看到size和byte的关系为$byte = 2^{size}$

只请求全数据宽度的master可以省略其AxSIZE输出,对应的slave必须在其输入的AxSIZE通道输入对应数据宽度的值。

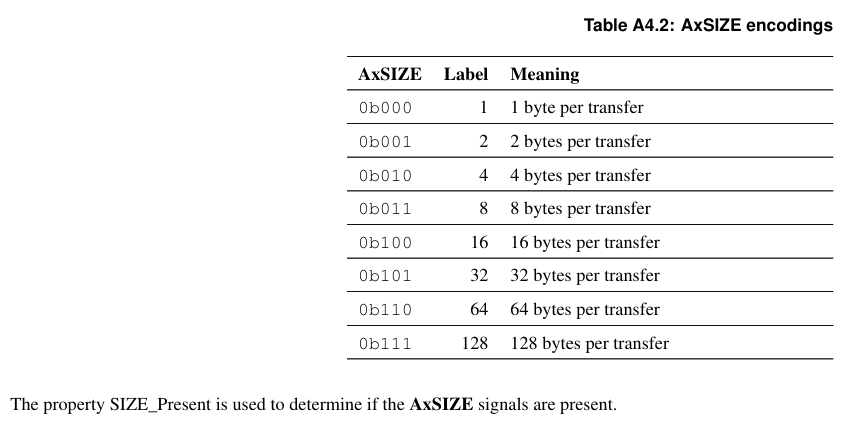

4.1.2 Length attribute

Length属性定义了每笔事务(transaction)中的transfer数量。

$Size \times Length$ 是每笔事务可以传输的最大字节数。

如果地址未对齐或存在置低的写入选通(write strobe),则传输的实际字节数可以低于 Size x Length。

一个Master必须根据Length的大小来发送写传输数据。

一个Slave必须根据Length的大小来发送读传输数据。

在读请求通道和写请求通道中,Length 被AWLEN和ARLEN确定,本spec中,AxLEN表示AWLEN和ARLEN.

只请求length为1的master可以省略其AxLEN输出,对应的slave必须在其输入的AxLEN通道的输入值设置为0x00。

以下规则被施加给length:

- 对wraping bursts,Length可以是2,4,8,16

- 对fixed bursts,Length最大可以达到16

- 一笔事务不可以超过4KB的地址上限

- 不支持提前终止传输事务

任何组件都不能提前终止事务。但是,为了减少 write transaction 中的数据传输数量,Manager 可以通过置低所有 write strobes 来禁用进一步的写入。在这种情况下,Master必须完成事务中的剩余传输。在读取事务中,Manager 可以丢弃读取数据,但它必须完成事务中的所有传输。

4.1.3 Maximum nubmer of bytes in a transaction

一笔事务的最大字节数为4KB。然而,很多Master发起的事务都低于这个值。

一个Slave或者interconnect可以会从这个信息中受益。例如,一个Slave可以增加一些decode逻辑。一个interconnect可以避免burst splitting,如果它知道一笔事务不会超过4KB的边界

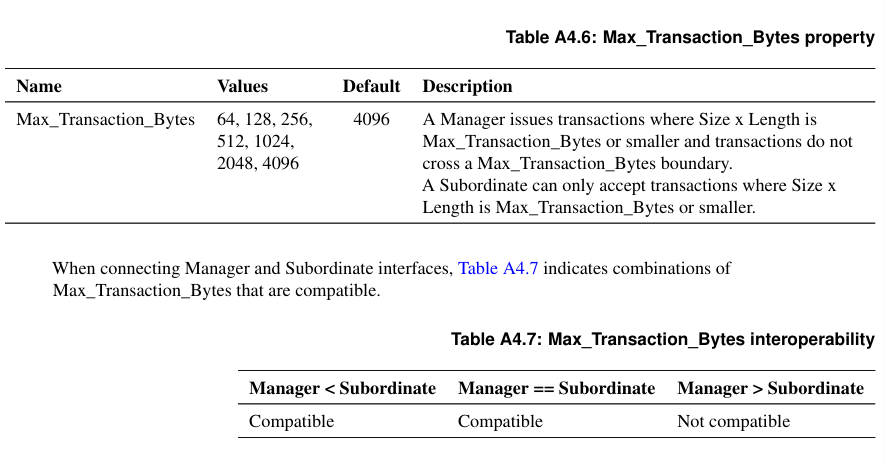

Max_Transaction_Bytes属性定义了一笔传输的最大字节数,如下所示:

4.1.4 Burst attribute

Burst属性描述了每笔传输事务中的transfer 地址是如何增加的。一共有3种不同的burst模式:

FIXED

这种Burst被用来重复的访问同一地址,例如读空或写满一个FIFO。

- 每个buret transfer的地址相同

- 所有transfer的有效byte lanes 固定不变。然而,在这些byte lane之内,每次传输由WSTRB选通的实际字节可以不同。

- burst的最大length可以达到16

- FIXED 突发类型只能与 WriteNoSnoop 或 ReadNoSnoop 操作码一起使用。

INCR

在这种BURST模式下,每个transfer的地址是前一次transfer地址的递增。例如,对一个对齐的起始地址,Size为4bytes时每次的地址都是前一次+4.这种burst模式被用来进行常规的memory顺序访问。

WRAP(wrapping)

此 Burst 类型类似于 INCR,不同之处在于,如果达到地址上限,地址将回绕到较低的地址。此外还需要施加以下约束:

- 起始地址必须与每次transfer的size对齐

- burst的Length必须是2,4,8或16

wrapping transaction的行为如下:

- 事务访问的最低地址是与要传输的数据的总大小(Size * Length)对齐的起始地址。 此地址定义为wrap boundary

- 每次传输后,地址的递增方式与 INCR 突发相同。但是,如果此递增的地址为 ((wrap boundary)+ (Size * Length)),则地址将回绕到wrap boundary

- 事务中的第一次传输可以使用高于 wrap boundary的地址,但要遵守适用于wrap transactions的限制。当第一个地址高于 wrap boundary时,地址将回绕。此种Burst 类型用于cache line的访问。

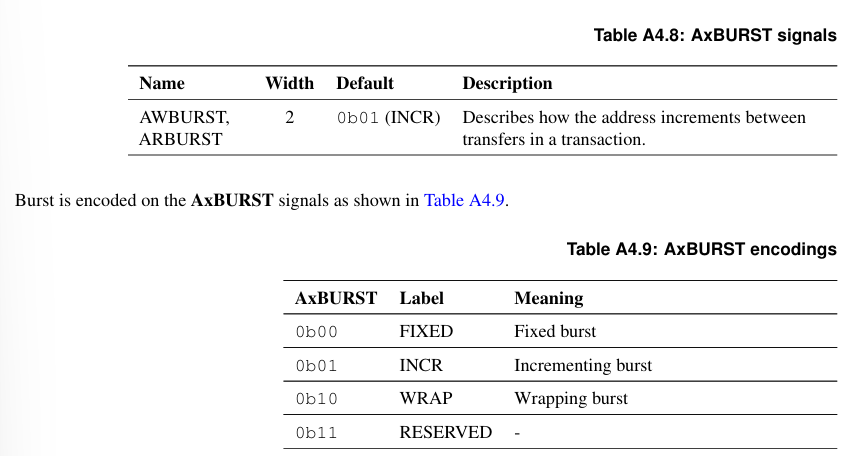

Burst 分别使用写入请求和读取请求通道上的 AWBURST 和 ARBURST 信号进行通信。在本规范中,AxBURST 表示 AWBURST 和 ARBURST。

FIXED burst由于并不常用,可以增加一个 Fixed_Burst_Disable属性来指示是否支持FIXED burst.

4.1.5 Transaction address

本节提供用于确定各个transaction中transfer地址和byte lane的方法。

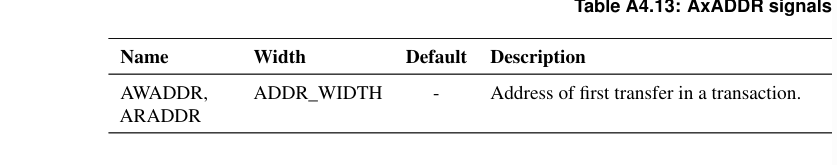

一个transaction的起始地址用AxADDR信号标识:

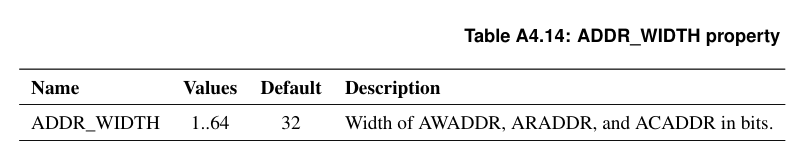

Address Width

ADDR_WIDTH用于定义地址的位宽

协议支持拥有物理地址空间大小的组件之间的通信。这些具有不同物理地址空间大小的组件必须遵循以下传输规则:

- 具有较小物理地址空间的组件必须位于较大物理地址空间的对齐窗口中。通常,窗口位于较大的物理地址空间的底部。但是,对于具有较小物理地址空间的组件,将其放置在较大物理地址空间内的偏移窗口中是可以接受的。

- 向外的传输事务必须将高位地址补齐。

- 向内的传输必须经过检查:

地址窗口内的transaction删除了高阶地址位

没有所需的高阶地址位的transaction将被抑制。

4.1.6 Transaction equation

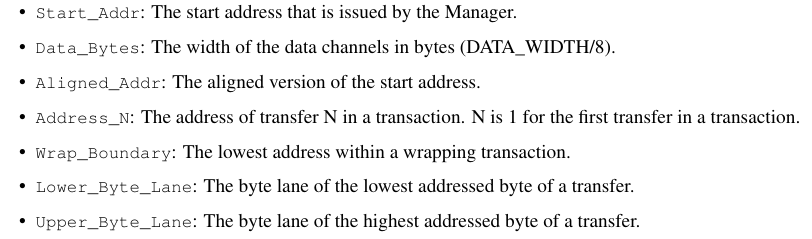

以下公式用于帮助确定transaction中每个transfer的地址和有效的data byte lane。

略

4.1.7 Pseudocode description of the transfers

略

4.1.8 Regular transaction

每笔transaction中可以有不同的burst,size和length组合。但是对于一些简化的设计可以只支持上述组合的一些子集。这样可以减小设计的负责程度。

如果一个transaction被定义为Regular,它应当具有以下熟悉:

- Length即transfer的数量为1,2,4,8,16

- 如果Length大于1,Size的值与data channel相同

- Burst为INCR 或 WRAP,而非FIXED

- 对INCR类型的transaction,地址与transaction container对齐

- 对WRAP类型的transaction,地址与size对齐。

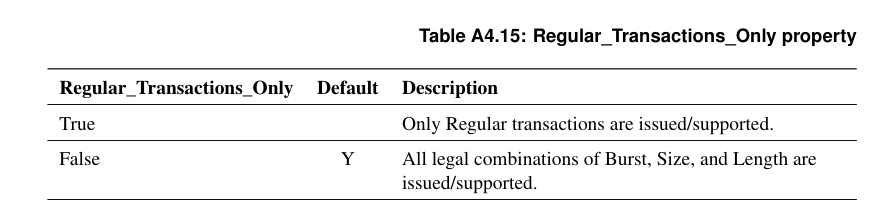

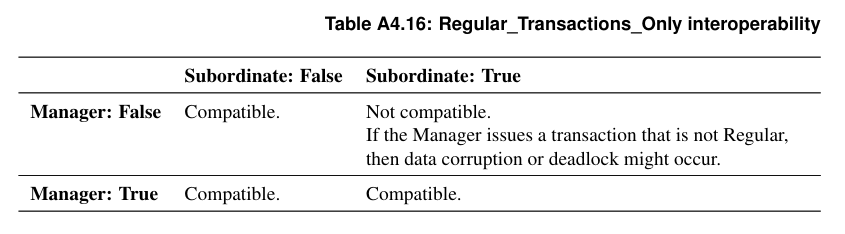

Regular_Transactions_Only 属性用于标识Master或Slave仅支持Regular transaction

4.2 Write and read data

本节描述不同大小的AXI读写通道以及interface如何实现mixed-endian和非对齐传输

4.2.1 Write Strobe

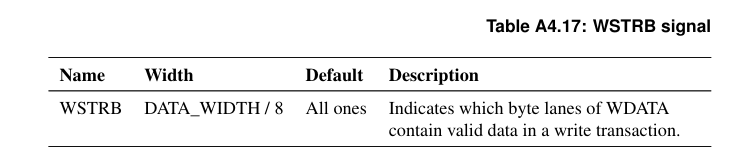

WSTRB信号携带哪些write data channel被选通的信息。

每8Bits的data对应1bit的strobe信号,WSTRB[n]对应WDATA[8n+7:8n]